# Development of Secure IoT Based on Modern Microcontrollers

Juraj Haluška

Bachelor's thesis May 2017 Technology, communication and transport Degree Programme in Software Engineering

Jyväskylän ammattikorkeakoulu JAMK University of Applied Sciences

#### Description

| Author(s)<br>Haluška, Juraj                                                                                                                                                                                     | Type of publication<br>Bachelor's thesis                                                                                                                                 | Date<br>May 2017                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Haluska, Juraj                                                                                                                                                                                                  | Number of pages                                                                                                                                                          | May 2017<br>Language of publication:                                                                                              |

|                                                                                                                                                                                                                 | 57                                                                                                                                                                       | English                                                                                                                           |

|                                                                                                                                                                                                                 |                                                                                                                                                                          | Permission for web                                                                                                                |

| Title of publication                                                                                                                                                                                            |                                                                                                                                                                          | publication: yes                                                                                                                  |

| Title of publication Development of secure IoT bas                                                                                                                                                              | ed on modern microcontrolle                                                                                                                                              | rs                                                                                                                                |

|                                                                                                                                                                                                                 |                                                                                                                                                                          |                                                                                                                                   |

| Degree programme<br>Information and Communications                                                                                                                                                              | Technology                                                                                                                                                               |                                                                                                                                   |

| Supervisor(s)<br>Mieskolainen, Matti                                                                                                                                                                            |                                                                                                                                                                          |                                                                                                                                   |

| Assigned by<br>Kotkansalo, Jouko                                                                                                                                                                                |                                                                                                                                                                          |                                                                                                                                   |

| Description                                                                                                                                                                                                     |                                                                                                                                                                          |                                                                                                                                   |

| Firstly, it analyses the available<br>also describes the most suitable<br>discusses the basics of software<br>and architectures were used to<br>The IoT device was developed of<br>microcontroller based on ARM | e microcontrollers on the marke<br>e development strategies. The r<br>develop an IoT device with end<br>on a prototyping board Nucleo-<br>architecture. The remote contr | et for this purpose and<br>most popular technologies<br>crypted data transfer.<br>F767ZI which runs on a<br>rol of the device was |

| implemented by exposing REST<br>server and the whole communi<br>integration, an open source libr<br>atmospheric pressure sensors we<br>these sensors was stored on an                                           | cation was secured by SSL/TLS<br>rary mbed TLS was used. Humic<br>vere connected to the device a                                                                         | protocol. For SSL/TLS<br>lity, temperature and                                                                                    |

| This data is available through R<br>mbed OS operating system with<br>web application was developed<br>Angular2 framework with UI lib                                                                            | n RTOS functionality. For a dem<br>I. This application was program                                                                                                       | onstration of RESTful API, the                                                                                                    |

| The result of the thesis is an int integrated into real IoT application                                                                                                                                         | •                                                                                                                                                                        | <b>c</b> ,                                                                                                                        |

| Keywords ( <u>subjects</u> )<br>IoT, mbed OS, mbed TLS, securi                                                                                                                                                  | ity, ARM, microcontroller, REST                                                                                                                                          | , HTTPS                                                                                                                           |

| Miscellaneous                                                                                                                                                                                                   |                                                                                                                                                                          |                                                                                                                                   |

Miscellaneous

# Contents

| 1 | Intr | oduc | tion                                  | 3  |

|---|------|------|---------------------------------------|----|

|   | 1.1  | Moti | ivation                               | 3  |

|   | 1.2  | Obje | ective                                | 3  |

| 2 | Mic  | roco | ntrollers                             | 5  |

|   | 2.1  | Wha  | at microcontrollers are               | 5  |

|   | 2.2  | Hist | ory and presence                      | 6  |

|   | 2.2  | ARN  | A and their portfolio                 | 8  |

|   | 2.3  | ARN  | I Cortex-M series                     | 10 |

|   | 2.4  | Cort | tex-M7 core                           | 11 |

|   | 2.4. | 1    | Instruction set                       | 11 |

|   | 2.4. | 2    | Interrupt controllers                 | 11 |

|   | 2.4. | 3    | SysTick timer                         | 12 |

|   | 2.4. |      | Extensional buses                     |    |

|   | 2.4. |      | Debugger interfaces                   |    |

|   | 2.4. |      | Computation modules                   |    |

|   | 2.4. |      | Memory protection unit                |    |

|   |      |      | ce of microcontroller                 |    |

| 3 | Sof  |      | e of microcontroller                  |    |

|   | 3.1  |      | nmon software strategies              |    |

|   | 3.2  |      | ed OS                                 |    |

|   | 3.2. |      | Task management                       |    |

|   | 3.2. | 2    | I/O and interfaces                    | 26 |

|   |      |      | Networking                            |    |

| 4 | Net  |      | security                              |    |

|   | 4.1  |      | · · · · · · · · · · · · · · · · · · · |    |

|   | 4.1. |      | Roles                                 |    |

|   | 4.1. |      | Structure                             |    |

|   | 4.1. |      | Session resumption                    |    |

|   | 4.2  |      | ору                                   |    |

|   |      |      | PS                                    |    |

| 5 | •    |      | entation                              |    |

|   | 5.1  | -    | tem architecture and technologies     |    |

|   | 5.2  | Soft | ware on Nucleo board                  | 40 |

| 5.2     | .1   | Threads                              | 40 |

|---------|------|--------------------------------------|----|

| 5.2     | .2   | TCP Sockets                          | 41 |

| 5.2     | .3   | mbed TLS Integration                 | 42 |

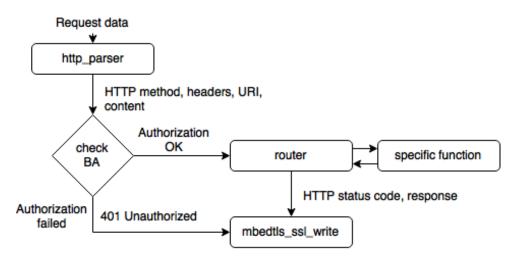

| 5.2     | .4   | HTTP Server                          | 44 |

| 5.2     | .5   | IP whitelist and user authentication | 45 |

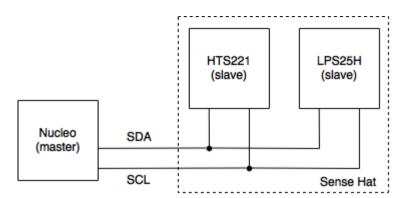

| 5.2     | .6   | Sensors                              | 47 |

| 5.3     | Clie | ent application                      | 49 |

| 6.1     | lss  | ues                                  | 51 |

| 6.2     | Dis  | cussion                              | 52 |

| 6.3     | Su   | mmary                                | 53 |

| Referer | nces |                                      | 54 |

2

### 1 Introduction

#### 1.1 Motivation

The Internet of Things (IoT) is increasingly set to become an inherent part of a human's everyday life. Today, there is a great number of objects that are connected to the internet already. For example, household appliances, vehicles, health and sleep monitoring devices, weather stations, heating units, etc. The connection of elementary things used every day on a network provides many benefits and simplifications of a human's life. As the popularity of IoT is rapidly rising, concerns have been raised about security and privacy. IoT devices could monitor sensitive information which no one wants to share with the unwanted subjects. Another issue with connecting things to the internet is the taking of control over the device by an unprivileged person. In some cases, this could result in catastrophic consequences. The rising popularity of IoT has a strong foundation in recent developments in microcontroller area. In the last decade, microcontrollers based on cores with ARM architecture have become very successful in areas of IoT. One of the main features of these microcontrollers is low power consumption, which is demanding due to continuous operation of IoT devices while providing relatively high computation power. Another significant advantage of ARMbased microcontrollers is a relatively low price and the availability of many kinds of prototyping boards. These boards give the developers' ability of rapid product development.

#### 1.2 Objective

This thesis focuses on the development of the IoT device driven by a modern microcontroller with the emphasis on security aspects. The first part of the thesis contains an analysis of microcontrollers available on the market and gives a brief overview of their hardware and architecture. There are also mentioned common strategies, how software for microcontrollers can be designed with or without the operating system. The second part of the thesis describes confidential information transfer over the internet using TLS. The last and main objective of this thesis is the development of an embedded system based on prototyping board Nucleo-F767ZI from STMicroelectronics. This system shall provide a web server secured by TLS, a simplistic HTTPS API, and web interface for simple control of board's peripherals.

## 2 Microcontrollers

#### 2.1 What microcontrollers are

Microcontrollers are small, integrated circuits which can be considered as selfcontained systems with a CPU, memory and peripherals (Heath 2002). Microprocessors known from classic personal computers do not contain memory and peripherals, which is why they need external ones connected via some kind of a bus system. On account of the fact that microcontrollers contain everything needed to form a computer, in most cases the only one necessity to make them work is to provide a software for them (Heath 2002). "Microcontrollers are designed to perform specific tasks. Specific means applications where the relationship of input and output is defined. Depending on the input, some processing needs to be done and output is delivered" (Choudhary 2017). Given that the applications of microcontrollers are very specific, they could be very optimized, and therefore they significantly reduce sizes and costs. They do not need such fast CPU as can be found in personal computers and they also have much smaller memory requirements. Since microcontrollers do not require rich resources, their power consumption is very small. This gives the ability to run microcontrollers from batteries and in some cases, they can run on battery uninterrupted for years.

Very important components of microcontrollers are peripherals. Peripherals give microcontroller the ability to interact with the surrounding environment and they can help the CPU with some functionality. Modern microcontrollers contain plenty of peripherals which can be used optionally due to the current needs of a particular application. Examples of the most common peripherals are listed as follows (Electronics hub 2015):

- GPIO general pin input output

- ADC analog to digital converter

- Serial protocol controllers SPI, UART, I2C

- Timers

- Memories RAM, Flash, EEPROM

There are also many other peripherals available, however, their presence in microcontrollers depends on the choice of particular models and also on the manufacturer. The availability of many kinds of peripherals, low power consumption, small size and high possibility of software optimization are the main factors why use microcontrollers in IoT applications.

#### 2.2 History and presence

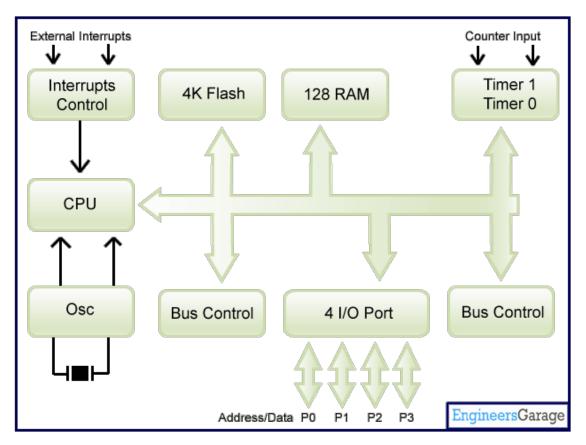

One of the most popular microcontrollers in history was the Intel 8051. This microcontroller was developed in 1980 by Intel Corporation and it was one of the first 8-bit microcontrollers. It can be seen in Figure 1. that this microcontroller was designed according to Harvard architecture. It means that it had separate memories for program and data, and those memories had their own address spaces. Later, the Intel 8051 was replaced by microcontrollers from many other companies such as Atmel, Infineon, NXP, Microchip (PIC), Texas Instruments. A widely recognized microcontroller architecture is 8-bit Atmel AVR. This architecture is still recognized nowadays because of its simplicity and also because Atmel AVR microcontrollers are used in a popular hobbyist platform - Arduino.

When 8-bit microcontrollers became no longer sufficient for certain tasks, 16bit microcontrollers were developed and replaced them. They became the largest volume MCU category in 2011 (IC Insights 2013). Nowadays, there are microcontrollers available which architectures are based on 32-bit word size. Architectures with wider word size provide fewer restraints on resources, particularly memory and the width of registers used for doing arithmetic and logical operations. This feature gives the ability to perform real-time operations on high precision data. These days, 32-bit microcontrollers are mainstream. There are still some microcontroller manufacturers, which use their own 32-bit architectures, however the majority of them rely on processor cores which are designed by ARM Holdings. ARM based microcontrollers are the most popular ones. They are very favored because of extremely low power consumption and software support from ARM Holdings. Another advantage of ARM cores is portability. Because of standards (CMSIS) defined by ARM Holdings, it is much easier to move from one MCU to another. 32-bit microcontrollers with ARM cores provide more options for developers while they can still maintain comparable power consumption with the old-fashioned 8-bit MCUs (STMicroelectronics 2017).

Figure 1. Block diagram of Intel 8051 (EngineersGarage 2017)

#### 2.2 ARM and their portfolio

ARM is an acronym of Advanced RISC Machine. It is a designation of processor architecture which has become very famous in the last years. The high popularity of ARM architecture is caused by the low power requirements of processors based on it. With over 100 billion ARM processors produced as of 2017, ARM is the most widely used processor architecture in terms of quantity produced (Wikipedia 2017). ARM architecture is developed and designed by a British company called ARM Holdings. Their main business interest is in the design of ARM architecture based processor cores but they design software solutions also. ARM Holdings does not manufacture processor cores themselves, they just sell the design of cores to other companies, usually semiconductor manufacturers. Then, they embed processor cores from ARM Holdings into their own products (ARM 2017).

As mentioned earlier, ARM is RISC kind of processor. Thanks to RISC design approach, the actual implementation of a processor requires less transistors than typical CISC processors. This approach reduces costs, heat and power consumption (Wikipedia 2017). Most of the ARM cores use 32-bit word width, however, the newest variation of ARM architecture (ARMv8-A) supports also 64-bit word width. The current portfolio of ARM cores can be divided into four families based on different use cases (ARM 2017).

#### a) ARM Cortex-A Series

In this family, there are cores designated for high level performance applications. Cortex-A processors offer support for a range of full operating systems including Linux, as well as others requiring a memory management unit such as Android, Chrome and MontaVista (ARM 2017). The processors in this family use ARMv7-A or ARMv8-A architectures, including their variations, and some of them support multi-core designs. The intended applications of ARM Cortex-A Series are (ARM 2017):

Smartphones

- Tablets and Readers

- Automotive

- Satellite receivers

- Wearables

- Home gateways

- Robotics

b) ARM Cortex-R Series

"The ARM Cortex-R real-time processors offer high-performance computing solutions for embedded systems where reliability, high availability, fault tolerance and/or deterministic real-time responses are needed. Cortex-R processors are used in products where performance requirements and timing deadlines must always be met. In addition, Cortex-R processors are used in electronic systems which must be functionally safe to avoid hazardous situations, for example, in medical applications or autonomous systems" (ARM 2017). Common applications of Cortex-R processors are (ARM 2017):

- Industrial

- Home

- Enterprise

- Cameras

- Storage

- Automotive

- Medical equipment

- Military

#### c) ARM Cortex-M Series

The processors in this family are smaller and come with the lowest power consumption of ARM products. These processors are optimized for deterministic real-time embedded processing and microcontroller application. ARM Cortex-M processors use 32-bit ARMv6-M, ARMv7-M and ARMv8-M architectures. The intended applications of processors from this family are (ARM 2017):

- Wireless sensors

- Smart watch

- Home automation

- Medical instruments

- Retail

- Industrial

- Smart watch

- Smart lighting

#### d) SecurCore

SecurCore is a family of 32-bit processors based on architectures ARMv6-M and ARMv7-M. They are derived from ARM Cortex-M processors, in addition, they contain anti-tampering mechanisms. Therefore, these cores are designed for use in highly secure applications. Some examples of use cases are listed below (ARM 2017):

- Advanced payment systems

- Electronic tickets, passports

Transportation

• Smart and SIM cards

#### 2.3 ARM Cortex-M series

As mentioned before, cores from this family are the most suitable for microcontrollers, which is the reason why this thesis gives more attention to this family. The ARM offers following cores from Cortex-M family (ARM 2017):

a) Cortex-M0, Cortex M0+, and Cortex-M23

These cores are for applications requiring minimal cost, power and area. Cortex-M0+ is the improvement of Cortex-M0 core. It is fully compatible with Cortex-M0, the difference is reduced power consumption, increased performance and added memory protection unit. It is not recommended to use older Cortex-M0 cores in new products. Cortex-M0/0+ use 32-bit ARMv6-M architecture. Cortex-M23 is the newest member of the Cortex-M family. This core uses ARMv8-M architecture, and it includes TrustZone technology.

b) Cortex-M3, Cortex-M4, and Cortex-M33

These cores are for all applications where a balance between 32-bit performance and energy efficiency is desirable. Cortex-M3 is the oldest member of the Cortex-M family. This core is useful when middle-level performance is required without the need for special features such as digital signal processing or fast floating point operations. This features can be found in cores Cortex-M4 and Cortex-M33. Cortex-M33 also has built-in TrustZone technology (ARM 2017).

#### c) Cortex-M7

This is one of the newest cores available on microcontroller market. It was launched in 2014. Cortex-M7 is the most powerful core from Cortex-M family and it is fully binary compatible with Cortex-M3 and Cortex-M4 cores. It is possible to execute instructions from Cortex-M3/M4 on Cortex-M7. The main improvement is that it can run on a much higher frequency while maintaining double power efficiency in comparison with the older Cortex-M4 (ARM 2017).

#### 2.4 Cortex-M7 core

#### 2.4.1 Instruction set

This core supports execution of Thumb-1, Thumb-2 and special DSP instructions with saturated arithmetic. The Thumb-1 instruction set is the subset of the classic ARM instruction set. ARM instructions are 32-bit long; however, Thumb-1 are 16-bit long, which allows bigger code density. The disadvantage of Thumb-1 instructions is that some tasks which could be done by one ARM instruction take more Thumb-1 instructions. Thus, it is a compromise between the execution time and code density. Older cores were able to execute only one type of instructions, either Thumb-1 or ARM and it was necessary to switch between the two. Thumb-2 is technology which enables execution of Thumb-1 instructions with 32-bit long instructions also. This technology also adds conditional execution instruction. Thumb-2 technology combines code density of Thumb-1 instruction set and performance or ARM instruction set (Yiu 2010).

#### 2.4.2 Interrupt controllers

In older cores, when the interrupt occurred, the software was needed to determine the starting address of an interrupt handler. This caused the

interrupt processing to be relatively slow. In every Cortex-M processor, there is NVIC which is a solution to that problem. Vectored interrupt support means that the interrupt handler address is saved in memory relating to its source. Thus, there is no need to perform additional software processing when an interrupt occurs. It is faster to process the interrupt request. Nested interrupt support adds prioritization to interrupt sources (My Hobbies 2017). "When an interrupt occurs, the NVIC compares the priority of this interrupt to the current running priority level. If the priority of the new interrupt will override the current level, the interrupt handler of the new interrupt will override the currently running task" (Yiu 2010). In Cortex-M7, there is available optional Wakeup Interrupt Controller. The function of this controller is to wake up core from a deep sleep when almost all processor modules are powered down (ARM 2017).

#### 2.4.3 SysTick timer

SysTick is a configurable, countdown 24-bit timer. This timer might be used as a time base generator for real-time operating systems. Depending on the clock source, it could also serve as a counter. SysTick might be configured to generate an interrupt each time it reaches zero value; as an alternative, it can operate in polling mode. SysTick timer is optional and it is part of NVIC. (ARM 2017).

#### 2.4.4 Extensional buses

Cortex-M7 processor is designed according to Harvard architecture. It has two separate buses, one for instructions (I-TCM) and one for data (D-TCM). Both of these buses are designed to provide tightly coupled memory for the processor core. This approach causes low-latency access, thus there is no need for cache memories. Peripherals such as GPIO, Timers and UART might be connected to the core with two AHB-Lite buses. AXI-M is an interface designed for connection of the external memory system. External memories are usually slower than those connected with TCM buses (e.g. Flash memory), thus, there is a need for cache memories, which is the purpose of I and D caches in the Cortex-M7 processor (Freescale 2015).

#### 2.4.5 Debugger interfaces

Cortex-M7 processor has rich debugging possibilities. It contains ETM and ITM modules. ITM module enables printf style debugging, ETM gives the core real-time tracing of instruction and data. Another debugging module is DWT. "The DWT is an optional debug unit that provides watchpoints, data tracing, and system profiling for the processor" (ARM 2010). Debugging modules are connected to a debugger application via JTAG or SWD port. SWD is a newer alternative to JTAG. JTAG usually uses 5-pin port while SWD uses only two wires: one for bidirectional data, another for clock transmission. This technology is widely used in microcontrollers from STMicroelectronics and in addition to debugging, it is also used for memory flashing (ARM 2017).

#### 2.4.6 Computation modules

Cortex-M7 is enhanced by DSP and FPU modules. The presence of these modules means that instruction set of Cortex-M7 is extended by special instructions belonging to these modules. Examples of the most common DSP instructions are multiply and accumulate. These modules are useful for fast algorithm performance in e.g. audio encoding, motor control, voice and image recognition, graphics, and data processing.

#### 2.4.7 Memory protection unit

MPU is an inherent part of secure systems. This unit allows segmentation of memory and control access to a particular segment. "The main purpose of memory protection is to prevent a process from accessing memory that has not been allocated to it. This prevents a bug or malware within a process from affecting other processes, or the operating system itself" (Wikipedia 2017).

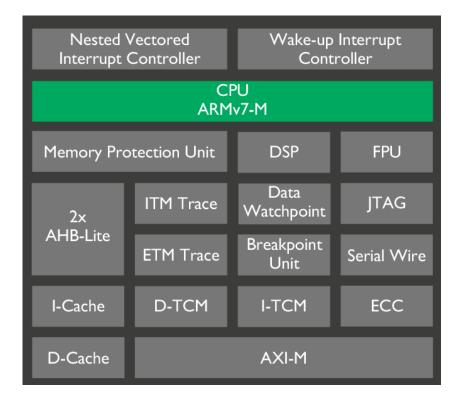

Modules mentioned above can be seen in following Figure 2. (ARM 2017):

Figure 2. Cortex-M7 module diagram (ARM 2017)

#### 2.5 Choice of microcontroller

The device developed in this thesis is required to run a web server with a secured connection. One step to get closer to secured web is by adding the encryption layer. Strong encryption algorithms need high computing rate. In the software of a web server, there is also need for fast string parsing, which is an operation consuming processor and memory. Because of high computing power, better power efficiency and availability of fast memory buses, a microcontroller with Cortex-M7 core was chosen for the practical part of this thesis.

ARM Cortex-M7 is quite a new core. As of April 2017, there are only three manufacturers which have caught up integrating Cortex-M7 in their products. The current manufacturers of Cortex-M7 based MCUs are Atmel (SAM E70, SAM S70, SAM V70), NXP (Kinetis KV5x) and STMicroelectronics (STM32 F7, STM32 H7). A significant role while choosing MCU was played by the availability of development materials and price. The chosen microcontroller is STM32F767ZI. This microcontroller is manufactured by STMicroelectronics,

and they also provide very cheap development board with it (Nucleo - F767ZI). MCU STM32F767ZI contains TRNG module, which is an integral part of systems, where encryption is involved. In addition, it also contains an Ethernet module. Therefore, there is no need to use an external Ethernet shield when implementing network connectivity. Another significant reason, why this board was chosen, is support of mbed OS. Barebone programming of ARM-based microcontrollers is not an easy task, especially for beginners. mbed OS significantly simplifies software development of embedded systems and in addition, it provides real-time operating system functionality, networking stack and security features (mbed 2017). Key features of STM32F767ZI (STMicroelectronics 2017):

- Core Cortex-M7 with 16 Kbytes I/D cache memories, frequency up to 216 Mhz, Dhrystone 2.1: 462 DMIPS/2.14 Mhz

- Up to 2 Mbytes of Flash memory organized into two banks allowing read-while-write

- SRAM: 512 Kbytes (including 128 Kbytes of data TCM RAM for critical real-time data) + 16 Kbytes of instruction TCM RAM (for critical realtime routines) + 4 Kbytes of backup SRAM

- Graphical accelerator, hardware JPEG coder/decoder, TFT and DSI display controllers

- Low power modes

- 3×12-bit 2.4 MSPS ADC up to 24 channels, 2×12-bit D/A converters

- DMA, Ethernet, 4x I2C, 4x USART, 4x UART, 6x SPI, 3x CAN, 2x SDMMC, 2x USB controller, 18 Timers, 168 I/O ports

- True random number generator

- CRC calculation unit

- Real time clock

- 96-bit unique ID

Following figure (STMicroelectronics 2017) shows all blocks of STM32F767ZI:

| System<br>Power supply<br>1.2 V regulator                                                                                                                     | Chrom-ART Accelerator™<br>JPEG Codec Acceleration<br>ART Accelerator™                                                                   | 2-Mbyte dual<br>bank Flash<br>512-Kbyte SRAM +<br>16-Kbyte ITCM RAM<br>FMC/SRAM/NOR/NAND/                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POR/PDR/PVD<br>Xtal oscillators<br>32 kHz + 4 ~26 MHz<br>Internal RC oscillators<br>32 kHz + 16 MHz                                                           | Cache I/D 16+16 Kbytes                                                                                                                  | SDRAM<br>Dual Quad-SPI<br>94-byte + 4-Kbyte<br>backup SRAM<br>1024-byte OTP                                                                                             |

| PLL<br>Clock control<br>RTC/AWU<br>1x SysTick timer<br>2x watchdogs<br>(independent and<br>window)<br>82/114/140/168 I/Os<br>Cyclic redundancy<br>check (CRC) | ARM<br>Cortex-M7<br>216 MHz                                                                                                             | ConnectivityTFT LCD controllerHDMI-CEC6x SPI, 3x I²S, 4x I²CCamera interfaceEthernet MAC 10/100with IEEE 1588MDIO slave3x CAN 2.0B1x USB 2.0 OTG FS/HS                  |

| Control<br>2x 16-bit motor control<br>PWM synchronized<br>AC timer<br>10x 16-bit timers<br>2x 32-bit timers                                                   | Floating point unit<br>(FPU)<br>Nested vector<br>interrupt<br>controller (NVIC)<br>JTAG/SW debug/ETM<br>Memory Protection Unit<br>(MPU) | 1x USB 2.0 OTG FS<br>2x SDMMC<br>4x USART + 4 UART<br>LIN, smartcard, IrDA,<br>modem control<br>2x SAI<br>(Serial audio interface)<br>SPDIF input x4<br>DFSDM<br>Analog |

| LP timer                                                                                                                                                      | AXI and Multi-AHB<br>bus matrix<br>16-channel DMA<br>True random number<br>generator (RNG)                                              | 2x 12-bit, 2-channel DACs<br>3x 12-bit ADC<br>24 channels / 2.4 MSPS<br>Temperature sensor                                                                              |

Figure 3. STM32F767ZI module diagram (STMicroelectronics 2017)

# 3 Software of microcontroller

As mentioned in the first chapter, microcontrollers are small, self-contained systems the role of which is to perform specific tasks where the relationship between input and output is defined (Choudhary 2017). This makes the software of microcontrollers also very specific. In the past, the architecture of microcontrollers was much simpler than these days, therefore, they could be programmed in assembly language and without the need for an operating system. With the increasing complexity of microcontrollers, it has become impossible to write software purely in assembly language. These days, there are very good C/C++ compilers available, which simplifies the whole software design and enables to implement operating systems for microcontrollers. It should be mentioned that assembly language is still used, however, only in very hardware specific setup procedures, which cannot be written in C/C++.

This chapter focuses on common software strategies and possibilities of using the operating system in microcontrollers. The last section of this chapter is about mbed OS, which is a relatively new project in the world of embedded systems. mbed OS significantly simplifies and accelerates the development of ARM-based microcontrollers software.

#### 3.1 Common software strategies

There are several strategies, how software of microcontroller can be designed. Choice of software strategy depends on complexity of particular application of microcontroller. There might be extremely simple systems, the task of which is just to respond when a button is pressed. On the other hand, there are more complex systems, e.g. systems which constantly monitor multiple parameters and need to adjust their outputs in real-time. Mentioned systems are very different, therefore their softwares are designed by different strategies. This chapter presents the most common software strategies used in MCUs.

Polling loop

This is the simplest strategy and it might be used in simple systems, the only task of which is to quickly react to some external events. An example of an event might be e.g. timer overflow, pressed the button, or incoming data. The principle of this strategy lies in repetitive checking if the event occurred. If the condition indicating an event is met, the microcontroller starts reacting to the event. After the reaction, the microcontroller is checking the condition again. The main disadvantage of this strategy is the waste of microcontroller's time while it is waiting for the condition to be met. Following figure is an example of simple polling loop implemented in C language.

# while(1) { if (buttonPressed) { reaction(); buttonPressed = !buttonPressed; } }

Figure 4. Example of polling loop in (C language)

#### b) Interrupt-driven

This strategy is in most cases a better alternative to polling loop because polling (also called busy waiting) is replaced by interrupts. An interrupt is a signal to the processor emitted by hardware or software indicating an event that needs immediate attention (Wikipedia 2017). When an interrupt occurs, the processor will suspend the execution of the current code and start the execution of code associated with the source of the interrupt. This code is usually called ISR. The main advantage of this strategy is that it does not waste processing time by busy waiting. The main loop might perform some useful processing while it can be interrupted at any time when needed. This approach is also called foreground/background system. Another advantage over the polling loop is that responses to events can be prioritized thanks to the interrupt mechanism. The Figure 5. shows an example of interrupt-driven system. In the left column, there is a main task which can be interrupted by interrupt controller and routines ISR\_1 or ISR\_2 will be executed instead.

| while(1) {         | void ISR_1 { | void ISR_2 { |

|--------------------|--------------|--------------|

| somethingUseful(); |              |              |

| }                  | }            | }            |

|                    |              |              |

Figure 5. Example of interrupt-driven strategy in (C language)

#### c) Cyclic executive

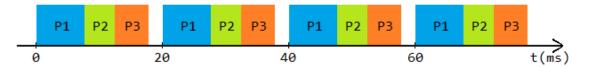

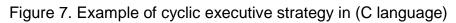

This strategy can provide the illusion of simultaneity by taking advantage of relatively short processes in a continuous loop (Ayav 2017). Cyclic executive works only if the processes are short enough and their execution time is constant. As an example, a system with three processes (P1, P2, P3) can be considered where P1 needs to be executed every 20 ms. Cyclic executive might be used in this case only if the sum of durations of processes P1, P2, P3 is less than 20 ms. The Figure 6. shows how processes in cyclic executive are executed. The main loop of cyclic executive program can be seen in Figure 7.

Figure 6. Diagram of process execution time in cyclic executive

#### d) Cooperative multitasking

Cooperative multitasking is a multitasking technique that enables two or more programs to cooperatively share the processing time and resources of the host processor (Technopedia 2017). This strategy is an extension of the cyclic executive, however, the difference is that processes are coded in the statedriven fashion (state machines). Processes are executed the same way as in cyclic executive but each time when the process is executed, it performs only one phase which corresponds to a certain state of that process. This phase has to be short enough to allow other processes to perform their phases in acceptable time. This approach allows processes to be more complex, but it is more difficult to synchronize them. Following figure presents an example of the two independent tasks in cooperative multitasking strategy.

| void P1() {                    | void P2() {                    |

|--------------------------------|--------------------------------|

| <pre>switch (P1_state) {</pre> | <pre>switch (P2_state) {</pre> |

| case START: break;             | case START: break;             |

| case REGULATE: break;          | case RECEIVE_DATA: break;      |

| case FINISH: break;            | case FINISH: break;            |

| }                              | }                              |

| }                              | }                              |

|                                |                                |

Figure 8. Example of processes in cooperative multitasking (C language)

#### d) RTOS

"Real time system is any system in which the time at which output is produced is significant. This is usually because the input corresponds to some movement in the physical world, and the output has to relate to that same movement. The lag from input time to output time must be sufficiently small for acceptable timeliness" (Daintith, J., Wright E. 2008). The acceptable timelines are often also referred to as deadlines. An example of real time system might be a digital audio mixer. This device is used by sound engineers and musicians for live performances. Audio mixer receives an audio from multiple sources (e.g. microphones, musical instruments) and its task is to mix those sources into one or more channels. Mixed audio is then amplified and played back to the audience through speakers. To obtain an effect of a live show (that an audience will not notice a delay between what they see and what they hear), it is required to keep the delay between recording and playing back under 20 ms. Thus the time, under which the digital mixer must mix and process each bunch of samples, is 20 ms. This is the real time system the deadline of which is 20ms. If this deadline is not met, the quality of live performance is being degraded. Real time systems could be classified into three categories:

#### 1) Hard Real Time

In these systems, the processing has to be done before a deadline. If the deadline is not met, it will result in catastrophic consequences. As examples of hard real time might be e.g. air traffic control systems, car braking system, navigation system of missile, self-driving car (Ayav 2017).

#### 2) Soft Real Time

Soft real time systems are those where missing a deadline causes a degradation of a system's quality instead of a catastrophe. An example of this system might be a digital audio mixer, which was already mentioned previously (Ayav 2017).

#### 3) Firm Real Time

These systems are similar to hard real time systems in a manner that they have hard deadlines defined, however, some low probability of missing a deadline can be tolerated. An example of this might be an automated assembly line (Ayav 2017).

From the included examples of real time systems above might be seen that they are often used in embedded applications. This is the point where real time operating systems occur. The real time operating system is a kind of operating system where tasks are scheduled in a fashion that they can meet their deadlines. The characteristics of real time system in an embedded application can be obtained by using one of the strategies mentioned in this chapter, however, real time operating systems simplify the software design. The common implementations of real time operating systems take care of process scheduling, IPC, memory allocation and memory protection, resource sharing and interrupt handling on software layer. Many of the available real time operating systems offer additional features such as device drivers, file systems, or networking stacks. These real time operating systems are often referred to as full-featured real time operating systems. As mentioned, real time operating systems are often used in embedded applications and therefore they are optimized to run on microcontrollers. The characteristics of the operating system and optimization for microcontrollers usually make usage of real time operating systems convenient in applications where real time system characteristics are not even required. A list of the most popular real time operating systems follows below:

- FreeRTOS

- RIOT

- eCOS

- μC/OS-III

- RTLinux

- VxWorks

- Keil RTX

- QNX

#### 3.2 mbed OS

Because of the high complexity of modern 32-bit microcontrollers, the development of barebone software for them has become a difficult task. There are several hardware-related configurations involved, e.g. clock distribution for peripherals, PLLs and frequency dividers, power distribution, bus configurations. Fortunately, there are solutions which abstract away hardwarerelated issues from programmers and even more, they also bring to a software features, which simplifies the whole development. One of the solutions is presented in this chapter and it is called mbed OS. mbed OS is a modern, open source operating system designated for IoT devices running on microcontrollers with ARM Cortex-M cores. It is collaboratively developed by ARM Holdings and their partners. mbed OS is a full-featured RTOS programmed in C/C++. It contains a low level security kernel called mbed uVisor, RTOS based on Keil RTX, peripheral drivers, drivers for the external devices and TCP/IP stack. For a quick and easy development of a secure IoT application, mbed OS supports many development boards from several manufacturers. These properties had a significant impact on the choice of the development board for the practical part of this thesis.

#### 3.2.1 Task management

mbed OS provides a comprehensive API for task management. An important part of this API is RTOS, an implementation of Keil RTX which allows the creation of programs simultaneously, performing multiple functions and helps to create better structured and more easily maintainable applications (Keil 2017). RTOS in mbed OS handles the creation and destruction of threads and safe inter-thread communication as well. It is composed of the following classes (mbed 2017):

#### a) Thread

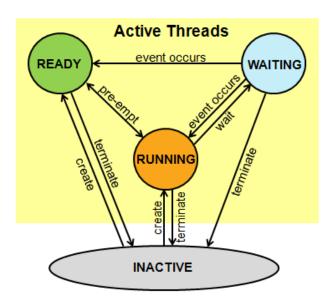

"The Thread class allows defining, creating and controlling thread functions in the system" (mbed 2017). The thread can be in one of the following states (Figure 9.): Running, Ready, Waiting and Inactive. It is possible to configure the stack size and priority for each thread through their constructor (mbed 2017).

Figure 9. States of thread in mbed OS RTOS (mbed 2017)

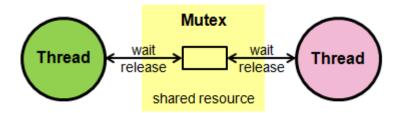

#### b) Mutex

Mutex (mutual exclusion) is a locking mechanism of the operating system to protect shared resources. It ensures thread synchronization. Resource (e.g. variable, a bunch of memory, etc.) might be locked by mutex; it can be then modified only by the thread which has locked it. Mutex operations in mbed OS are: lock, trylock and unlock. These operations can be called only by threads. The following figure (Figure 10) presents mutex mechanism and its operations.

Figure 10. Mutex mechanism (mbed 2017)

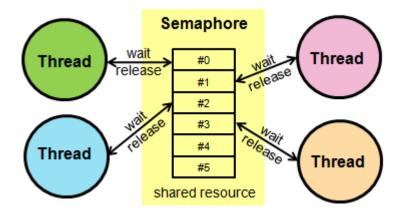

#### c) Semaphore

Semaphore is a mechanism for sharing a pool of resources of the same kind between multiple threads. The number (size of the pool) of resources which will be protected by semaphore is defined via its constructor. There are two operations associated with the semaphore: wait and release. Calling wait operation will appropriate one resource, or it will wait if the resource is not available. The release operation will release the resource so that it can be used by the other threads. Figure 11 shows how multiple threads can control the access to shared resources using the semaphore.

Figure 11. Semaphore mechanism (mbed 2017)

#### d) Signal

A signal is a simple tool for notification of events between threads. There are only two calls defined: wait and signal. The parameter of this calls is a flag which is the 4-byte integer. If one thread is waiting for a particular flag, other threads can interrupt that waiting by calling the signal on the same flag.

#### e) Queue and Mail

These classes provide a safe way of data transfer between threads. The data transfers between threads are often also referred to as messages. The queue allows sending messages which are 4-byte long (pointers or integers). "Mail works like a queue, with the added benefit of providing a memory pool for allocating messages (not only pointers or integers)" (mbed 2017).

In addition to RTOS specific functions, mbed OS has other built-in functions which might be used for task management:

#### a) Event loop

The event loop is a mechanism that can be used to defer the execution of the code to a different context. "In particular, a common use of an event loop is to postpone the execution of a code sequence from an interrupt handler to a user context" (mbed 2017). The ISRs are not thread-safe, thus it is recommended to divide them into two sections. One section, which is a part of ISR, should contain only time critical operations. The second section, the execution of which could be scheduled (some delay tolerance), should be deferred from ISR to user context using the event loop.

#### b) Time-based classes

The ticker class serves for calling a function repeatedly in a specified time interval. For calling a function only once after a specified delay, there is the Timeout class available. The last time-based class for task management is a Wait. "When Wait is called inside thread, the OS scheduler will put the current thread in waiting state, allowing another thread to execute" (mbed 2017). It is worth mentioning that there are other classes which work with the time, however, their functionality is not for task management. These classes are Time and Timer. Time class provides an interface of hardware real-time clock and it has functions for date conversions and formatting. For measurement of time intervals, there is Timer class available. Timer uses 32-bit signed integer for counting microsecond steps (mbed 2017).

#### 3.2.2 I/O and interfaces

The following table is an outline of API abstraction in mbed OS:

Table 1. I/O API in mbed OS (mbed 2017)

| Туре        | Class                                   | Description                                                                                                                                       |

|-------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog I/O  | AnalogIn<br>AnalogOut                   | read the voltage of an analog input pin set the voltage of an along output pin                                                                    |

| Digital I/O | DigitalIn<br>DigitalOut<br>DigitalInOut | read a single digital input pin<br>write to a single digital output pin<br>read and write to a single bidirectional digital pin                   |

| Bus I/O     | BusIn<br>BusOut<br>BusInOut             | read multiple pins as a single value<br>write a single value to multiple pins<br>read and write to multiple bidirectional pins                    |

| Port I/O    | PortIn<br>PortOut<br>PortInOut          | read pins from port as a single value<br>write a single value to pins in the port<br>read and write to multiple bidirectional pins in the<br>port |

| Interrupt   | InterruptIn                             | triggers an event when a digital input pin changes value                                                                                          |

| PWM         | PwmOut                                  | controls the frequency and duty cycle of PWM                                                                                                      |

mbed OS has also built-in drivers for following digital interfaces:

Table 2. Digital interfaces API in mbed OS (mbed 2017)

| Interface | Class         |

|-----------|---------------|

| UART      | Serial        |

| SPI       | SPI, SPISlave |

| 12C       | I2C, I2CSlave |

| CAN       | CAN           |

#### 3.2.3 Networking

The mbed OS has built-in drivers for Ethernet and Wi-Fi modules of many development boards. Communication with those modules is accomplished by corresponding classes - EthernetInterface and WifiInterface. As a default TCP/IP stack, mbed OS uses a lightweight open source project designed for embedded devices - Iwip. On the top of the TCP/IP stack, mbed OS provides a simple socket API. "It's a class-based interface, which should be familiar to users experienced with other socket APIs" (mbed 2017). The socket API works in the same way with both of the interface classes mentioned above. There are three important classes in socket API:

#### 1) UDPSocket

"The UDPSocket class provides the ability to send packets of data over UDP, using the sendto and recvfrom member functions. Packets can be lost or arrive out of order, so we suggest using a TCPSocket (described below) when guaranteed delivery is required" (mbed 2017).

#### 2) TCPSocket

"The TCPSocket class provides the ability to send a stream of data over TCP. TCP sockets maintain a stateful connection that starts with the connect member function. After successfully connecting to a server, you can use the send and recv member functions to send and receive data (similar to writing or reading from a file)" (mbed 2017).

#### 3) TCPServer

"The TCPServer class provides the ability to accept incoming TCP connections. The listen member function sets up the server to listen for incoming connections, and the accept member function sets up a stateful TCPSocket instance on an incoming connection" (mbed 2017).

#### 3.2.4 Development environment

There are basically three possible options, how microcontroller's software based on the mbed OS can be developed. The first development option is using the mbed CLI. "mbed CLI is the name of the ARM mbed command-line tool, packaged as mbed-cli. mbed CLI enables Git- and Mercurial-based version control, dependencies management, code publishing, support for remotely hosted repositories (GitHub, GitLab and mbed.org), use of the ARM mbed OS build system and export functions and other operations" (mbed 2017). The mbed CLI allows a simple import of libraries from the mbed repository, compilation using one of the available compilers (GCC ARM, ARM Compiler 5, IAR), and testing and source control, while the developers can still use their favorite text editor. The practical part of this thesis was developed using mbed CLI with a Geany text editor.

The second option is called mbed Online Compiler. It is the simplest way how to develop software with the mbed OS. mbed Online Compiler is in-browser IDE which provides the same functionality as mbed CLI with text editor added. Using the mbed Online Compiler avoids the need to install anything on the local computer, which is its main advantage.

The third option involves third-party toolchains. It is possible to export project files from mbed CLI and mbed Online Compiler to many of available IDEs. If the developer does not use IDE, or it is not supported, there is also the possibility to generate GNU Makefile. Then it can be used with one of the three mentioned compilers above. The list of supported IDEs (mbed 2017) is as follows:

- Keil uVision5

- IAR Systems

- Eclipse CDT/GNU ARM

- Atmel Studio

- Simplicity Studio

- DS-5

- LPCXpresso

- Kinetis Design Studio

- CooCox CoIDE

- e2studio

# 4 Network security

The internet is a place full of threats. The connection of objects to the internet makes them possible victims for attackers. When connecting objects to the internet, it is very important to ensure that the transmitted data cannot be read by unwanted subjects and that parties of communication are what they claim to be. There is a standardized way how to ensure security over the network. It is called Transport Layer Security (TLS) and it is used in practical part of this thesis to provide data protection and the identity of an IoT device.

#### 4.1 TLS

#### 4.1.1 Roles

TLS is a cryptographic protocol that provides security for devices connected to the network. TLS is a follower of the older SSL protocol and its newest version is TLS 1.2. "The primary goal of the TLS protocol is to provide privacy and data integrity between two communicating applications"(RFC 5246 2008). It is commonly used to secure web protocol (HTTPS), email communication, VoIP, Instant Messaging, remote login (SSH), etc. When the connection is secured by TLS, it has one or more of the following properties (Wikipedia 2017):

a) Privacy

The privacy of data is reached by encryption. Encryption is a mechanism which encodes information or messages so that only authorized parties can access it. "Encryption works by using a mathematical formula called a cipher and a key to convert readable data (plain text) into a form that others cannot understand (ciphertext). The cipher is the general recipe for encryption, and the key makes the encrypted data unique. Only parties with the unique key and the same cipher can unscramble it" (Sans 2011). For encryption, TLS offers several symmetric cipher algorithms, e.g., AES, Blowfish, Camellia, DES/3DES, XTEA, RC4 (mbed TLS 2017).

#### b) Identity

The identity of communicating parties is achieved by public-key cryptography. This property is optional, however, it is usually used at least by one party. TLS also uses public-key cryptography for the exchange of symmetric encryption key. Examples of these public-key cryptographic algorithms are RSA, DSA, D-H.

#### c) Integrity

For integrity check, TLS inserts to each message an authentication code (MAC). It is a mechanism that makes it possible to determine whether the data has been changed by an unwanted subject. MAC is a sort of checksum and it uses hash functions (e.g., SHA-1).

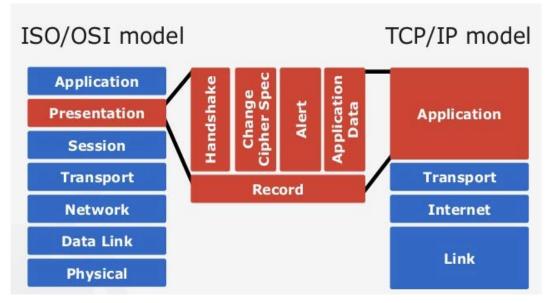

"One advantage of TLS is that it is application protocol independent. Higherlevel protocols can layer on top of the TLS protocol transparently" (RFC 5246 2008). Application protocol independent means that TLS is inserted between the application protocol (HTTP, SMTP, etc.) and the transport protocol (TCP). Figure 12 illustrates that TLS is represented as a part of the application layer in the common TCP/IP model.

Figure 12. ISO/OSI and TCP/IP models with TLS (Luedtke 2012)

#### 4.1.2 Structure

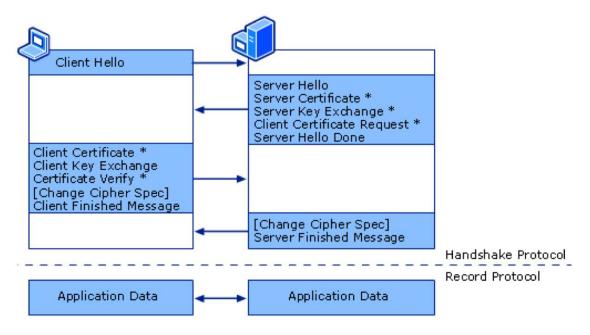

"The TLS protocol is composed of two layers: the TLS Record Protocol and the TLS Handshake Protocol" (RFC 5246 2008).

#### a) TLS Record Protocol

This layer communicates directly with the transport layer of TCP/IP model. The role of this layer is to process data from higher layers and to transmit them to the transport layer. The data processing operations performed by this layer are listed below (RFC 5246 2008):

- fragmentation/defragmentation

- compression/decompression

- MAC computation and verification

- encryption/decryption

- b) TLS Handshake Protocol

When the communication between a client and server begins, they must exchange and agree on the protocol version and cryptographic algorithms. The public-key encryption is used to transfer shared keys and optionally, one or both of communicating peers are authenticated. These procedures are handled by TLS Handshake Protocol, which works on the top of TLS Record Protocol. The steps involved in TLS Handshake Protocol (RFC 5246 2008) are listed as follows:

- "Exchange hello messages to agree on algorithms, exchange random values, and check for session resumption.

- Exchange the necessary cryptographic parameters to allow the client and server to agree on a premaster secret.

- Exchange certificates and cryptographic information to allow the client and server to authenticate themselves.

- Generate a master secret from the premaster secret and exchanged random values.

- Provide security parameters to the record layer.

- Allow the client and server to verify that their peer has calculated the same security parameters and that the handshake occurred without tampering by an attacker" (RFC 5246 2008).

Figure 13. TLS Handshake Protocol (Zoompf 2017)

If the handshake was successful, the TLS Record Protocol will set up the exchanged parameters and the TLS session is created. Now, the application protocol (HTTP, etc.) can start using the secured TLS Record Layer directly.

#### 4.1.3 Session resumption

The TLS Handshake Protocol involves the usage of an asymmetric cipher (public-key cryptography). Asymmetric cipher algorithms are more difficult than symmetric and require a more computing power. This brings a significant latency to the communication. For example, web browsers usually make multiple requests to the server in a row. Each request performs its own handshake and if there are more clients connecting to the same server, it will overload the server and will lead to DoS. In order to increase computational performance and to prevent DoS, TLS contains a mechanism called session resumption. This mechanism ensures a much faster handshake because performing the asymmetric cipher algorithm at each request is no longer needed. There are two ways of session resumptions in TLS (Lin, Z. 2015).

#### a) Session ID resumption

"Resuming an encrypted session through a session ID means that the server keeps track of recently negotiated sessions using unique session IDs. This is done so that when a client reconnects to a server with a session ID, the server can quickly look up the session keys and resume the encrypted communication" (Lin, Z. 2015). The disadvantage of session resumption by session ID is that the server has to store information according to the particular session. This disadvantage takes place only in cases where there is a significant number of clients using the session resumption of which the server has to keep track.

#### b) Session ticket resumption

In order to prevent the server from keeping session information to save its memory, an alternative to session ID resumption was developed. It is called session ticket resumption and the principle of this way is that the session information is stored on the client side instead of the server. "A session ticket is a blob of a session key and associated information encrypted by a key only known by the server. The ticket is sent by the server at the end of the TLS handshake. The clients supporting session tickets will cache the ticket along with the current session key information. Later the client includes the session ticket in the handshake message to indicate it wishes to resume the earlier session. The server on the other end will be able to decrypt this ticket, recover the session key and resume the session" (Lin, Z. 2015).

# 4.2 Entropy

Cryptographic algorithms use random number generators for the creation of keys. The whole power of cryptographic algorithms lies in the randomness of numbers provided by random number generators. Entropy is a term which expresses unpredictability or randomness of some system. Random number generators use entropy sources to generate random numbers. If the random number generator uses weak entropy, its output can be predicted and the security of the system can be compromised by attackers. Random number generators can be divided into two categories (Hoffman, Ch. 2014):

- Pseudo Random Number Generator (PRNG)

- True Random Number Generator (TRNG)

PRNGs use deterministic algorithms with some kind of seed to generate the random number. Since the deterministic algorithms are used, the number which was generated is not truly random. The output sequence of PRNG can be predicted, which makes it unusable in cryptographic algorithms. On the other hand, PRNGs are relatively fast and they can find their usage in many other applications (games, simulations, etc.) (Hoffman, Ch. 2014).

For cryptographic purposes, TRNGs are used. TRNGs produce sequences of numbers which are unable to predict. They are also called nondeterministic RNGs. TRNG depends on some unpredictable entropy source outside of any human control (STMicroelectronics 2016). These entropy sources are usually some physical events or phenomena, which behave randomly. As an example of these sources might be cosmic radiation, radioactive decay of an atom, and radio frequency noise. Due to the physical nature of these entropy sources, they are usually presented by some electronic device. Another example might be how Linux kernel generates a random number. Linux kernel combines multiple sources of entropy such as keyboard and interrupt timings, hard drive operations, noise in audio input, etc., which are hardly-predictable (Linux kernel 2005).

In general, the generation of true random number takes more time than the

generation of the pseudo random number. This is because truly random numbers are generated by measuring entropy, not with computing by some algorithm as it is done in pseudo random number generators. Slow generation of true random numbers would be especially true in microcontrollers, which suffer from lack of entropy sources in comparison with personal computers. Fortunately, microcontrollers designated for the usage in applications where security is demanded contain hardware modules for true random number generation. The microcontroller, which was chosen for the practical part of this thesis (STM32F767ZI) contains a true random number generator based on an analog circuit. "This circuit generates a continuous analog noise that will be used on the RNG processing in order to produce a 32-bit random number. The analog circuit is made of several ring oscillators whose outputs are XORed. The RNG processing is clocked by a dedicated clock at a constant frequency and for a subset of microcontrollers, it can also be clocked with a different value of frequency" (STMicroelectronics 2016). The hardware TRNG module in STM32F767ZI is used in the practical part of this thesis as a source of random numbers for TLS.

## 4.3 HTTPS

The device developed in this thesis communicates with the surrounding world through HTTPS, which is HTTP protocol secured by SSL/TLS mentioned in section 4.1. The default TCP/IP port of HTTPS communication is 443 and the URI uses 'https' protocol identifier instead of 'http'. HTTPS protocol was chosen for this thesis because it gives enough security and it is relatively simple to implement on embedded systems. However, the main reason why HTTPS was chosen is that it is very universal. The device can be controlled directly through the web browser or mobile application using a uniform API. The web browser application used for the control of the IoT device was implemented as a part of this thesis.

# 5 Implementation

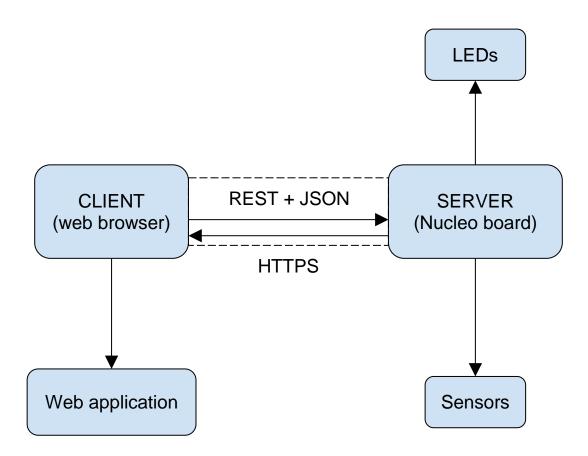

# 5.1 System architecture and technologies

As mentioned in the previous chapter, the HTTPS protocol was chosen for the communication between the client and server. The server is implemented on a Nucleo board with mbed OS, and the board exposes its functionality to the client through the RESTful API. The data exchanged between the client and server is in JSON format. The mentioned technologies were chosen because they are relatively simple and easily integrated into many of the modern applications. The client application developed in this thesis is web-browser based, however, the usage of the mentioned technologies allows to easily implement alternative client applications on the other platforms such as Android, iOS, etc. Figure 14 represents the top layer architecture of the system:

Figure 14. Diagram of system architecture

The web application is not provided to the client by a server implemented on the Nucleo board. The role of that server is just to expose its functionality by the RESTful API to the client. As shown in Figure 14, the web application is not a part of the server nor even a client. The web application might be stored on the client side, however, it might also be served to the client by an external web server.

"A RESTful API is a remote API that follows the REST style of software architecture" (McVetta 2012). REST stands for representational state transfer. The REST architecture can be used with other protocols than HTTP, however, it is mostly used with it. The REST API exposes resources of the server in a logical way, identified by the uniform resource identifier (URI). The URI structure of REST API usually represents the logical layout of the resources on the server side. For example, on a file server, it might represent the directory structure of the underlying file system. Data transferred by REST API is represented in various formats. The most common formats are JSON and XML which can easily model the objects of an underlying system. The REST API is stateless, which is a very important characteristic. Stateless means that the server does not keep information about the client. "Each request from any client contains all of the information necessary to service the request, and any session state is held in the client" (McVetta 2012). The REST API used on the web uses HTTP methods corresponding to CRUD operations. CRUD operations with corresponding HTTP methods are listed as follows (RestApiTutorial 2017):

| CRUD Operation | HTTP Method |

|----------------|-------------|

| Create         | POST        |

| Read           | GET         |

| Update         | PUT / PATCH |

| Delete         | DELETE      |

Table 3. CRUD operations and corresponding HTTP methods

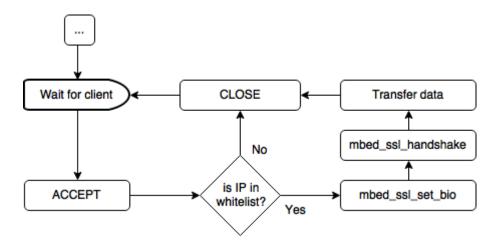

The following table, Table 4 shows an example on how IP addresses are manipulated in a server's whitelist using REST API (more details on whitelist implementation will be given further in this thesis).

| HTTP<br>Method | URI                           | Description                                     |

|----------------|-------------------------------|-------------------------------------------------|

| GET            | https://server/ip             | Get list of all IP addresses in whitelist       |

| POST           | https://server/ip/192.168.1.1 | Add IP address 192.168.1.1<br>to whitelist      |

| DELETE         | https://server/ip/192.168.1.1 | Remove IP address<br>192.168.1.1 from whitelist |

| PUT /<br>PATCH |                               | not implemented                                 |

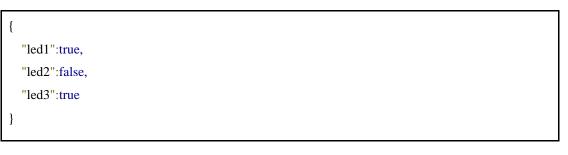

Table 4. REST API for manipulation of IP addresses in server's whitelist

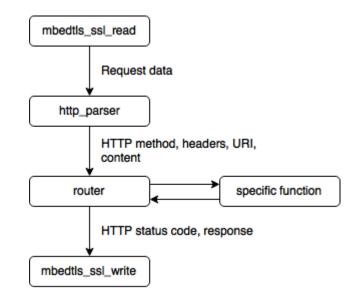

The data transferred between client and server using HTTP protocol is in the text form. The client application in this thesis is web-browser based and is programmed in JavaScript. It is very favorable to use JavaScript Object Notation (JSON) format for data exchange between the client and server because JSON is just a text format and JavaScript objects are easily converted to/from JSON. "JSON (JavaScript Object Notation) is a lightweight data-interchange format. It is easy for humans to read and write. It is easy for machines to parse and generate" (JSON 2017). "JSON is a text format that is completely language independent but uses conventions that are familiar to programmers of the C-family of languages, including C, C++, C#, Java, JavaScript, Perl, Python, and many others. These properties make JSON an ideal data-interchange language" (JSON 2017). The implementation of JSON in the server on Nucleo board is not a full implementation according to official document (RFC 7159) describing JSON format. Many of available opensource JSON parsers are too heavy for use in microcontrollers and use dynamic memory allocation. On account of the fact that the format of all JSON objects received by the server is known in a compile-time, a custom simplistic JSON parser was developed for the purposes of this thesis. This custom parser supports only non-nested key-value pairs, while it still maintains JSON formatting. An example of the JSON data acceptable by the server in this thesis can be seen in Figure 15:

Figure 15. Example of JSON used in the server developed on Nucleo board

# 5.2 Software on Nucleo board

## 5.2.1 Threads

The software on Nucleo board performs two tasks: serving content to the client via HTTPS, and reading and storing sensor values. The thread mechanism of mbed OS was utilized to attain multitasking. Currently, there are three threads implemented in software of Nucleo board:

- Main thread

- Server thread

- Sensor thread

The main thread is a thread which must be present in every mbed OS application. This thread is automatically executed after a system boot-up by mbed OS. The only role of this thread is to initialize global variables and to execute another two threads (Server and Sensor thread). The whole networking logic is implemented in the Server thread. The sensor thread reads the sensor's values at the specific time interval and stores them in the SD card's flash memory. Each of these threads is divided into two parts initializations and infinite loop.

#### 5.2.2 TCP Sockets

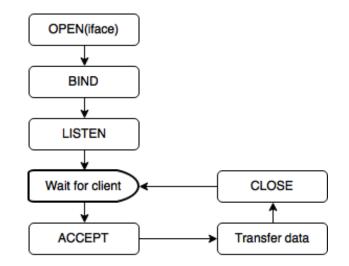

mbed OS socket mechanism was used for networking. There are two socket classes used to accomplish client-server communication. One class represents server (TCPServer), the other one represents the client (TCPSocket). Before the sockets can be used, the Ethernet interface has to be configured and connected. These steps are performed in the initializations part of the Server thread. The configuration of Ethernet interface involves setting up of network parameters such as IP address, network mask and gateway. After the network interface has been successfully configured and connected, it can be used by the TCPServer socket by calling the open method with that network interface as a parameter. After opening this socket, it has to be bound to the configured IP address and a TCP port. As soon as the application layer used on the top of this socket mechanism is HTTPS, port 443 is used. When the TCPServer socket has been successfully bound to an IP address and a TCP port, it can start listening for a client connection. Listening is realized in the infinite loop of the Server thread. When the client has connected to the server, the accept method will set-up the TCPSocket instance for the client and save the client's IP address in the SocketAddress structure. Now, the communication with the client can be done by calling recv and send methods on the client's TCPSocket instance. The following chart represents the socket utilization:

Figure 16. Flowchart of socket mechanism utilization in Server thread

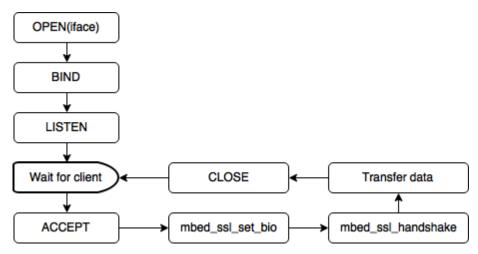

The integration of mbed TLS into the server application was realized in four steps:

1) Inclusion of mbed TLS header files

The first step was to include the needed mbed TLS header files in the main source file of the server application. The included files are listed in the following table:

Table 5. Included header files with description

| Header file | Description                                                    |  |

|-------------|----------------------------------------------------------------|--|

| ssl.h       | contains the most important functions for SSL/TLS              |  |

| entropy.h   | implements entropy accumulator                                 |  |

| ctr_drbg.h  | functions and macros for random number generation              |  |

| pk.h        | pk.h functions and macros for public and private keys handling |  |

| x509_crt.h  | functions and macros for certificate handling                  |  |

# 2) mbed TLS initialization

The initialization of mbed TLS is performed in the initializations part of the Server thread. This initialization involves the following steps:

- a) creation and initialization of mbed TLS structures

- b) certificate and private key parsing (they are stored in an internal flash memory of microcontroller)

- c) setting up parsed certificate and key to be used by TLS

- d) seeding and connection of entropy source to mbed TLS drbg random number generator

- e) setting up random number generator callback for TLS functions

- f) configuration of mbed TLS in server mode on the transport layer

- g) resetting TLS connection

The connection of hardware TRNG to mbed TLS entropy accumulator is realized by the implementation of glue functions and the indication of TRNG presence by "TRNG" flag in "targets.json" file (mbed OS file which describes each supported platform and its features). Luckily, these steps were done for Nucleo-F767ZI board by mbed OS developers, therefore the hardware TRNG will be used by mbed TLS entropy accumulator by default.

3) Implementation of callbacks for mbed TLS

As mentioned in section 4.1.1, SSL/TLS is built on top of the transport layer of the TCP/IP model. The connection between the TLS and transport layer is realized by two callback functions – the first for data receiving, the second for data sending. As soon as the socket mechanism was used, these callbacks are connected to the client instance of the TCPSocket returned by the accept function mentioned in the previous section. The type of these callbacks is defined in the "ssl.h" file. Figure 17 shows an implementation of those callback functions:

```