Srinivas Vijayanand Nayani

# DESIGNING SECURE SOLUTIONS FOR EMBEDDED SYSTEMS

# DESIGNING SECURE SOLUTIONS FOR EMBEDDED SYSTEMS

Srinivas Vijayanand Nayani Master's Thesis Autumn 2017 Information Technology Oulu University of Applied Sciences

# ABSTRACT

Oulu University of Applied Sciences Degree programme in Information Technology

Author: Nayani Srinivas Vijayanand Title of the master's thesis: Designing Secure Solutions for Embedded Systems Supervisor: Teemu Korpela Term and year of completion: Autumn 2017 Number of pages: 75

The aim of the thesis was to explore and develop an insight on various security aspects and practices that need to be considered while designing embedded products. The thesis was commissioned by Bittium Oy.

Design requirements were gathered from the customer of the project and they were further consolidated based on industry practices and standards. Solutions were developed in C language over Linux operating system using tools; Eclipse IDE, Hardware Debuggers, version control tools GIT and Gerrit for continuous integration methodology. The project was executed in the Iterative software development lifecycle model.

The project was completed successfully and delivered to the client by 2016. This thesis also extends the core topic a bit further by discussing some of the best practices for designing secure products and some of the future roadmaps and technologies in the area as part of conclusion.

Keywords:

Embedded security, Attacks and vulnerabilities, Trust execution environment, Multiple Independent Levels of Security, ARM TrustZone, Root of trust

# TABLE OF CONTENTS

| ABSTRACT                                                                      | 3  |

|-------------------------------------------------------------------------------|----|

| TABLE OF CONTENTS                                                             | 4  |

| VOCABULARY                                                                    | 7  |

| 1 INTRODUCTION                                                                | 9  |

| 2 DRIVERS FOR DEVICE SECURITY                                                 | 10 |

| 3 SECURITY ATTACKS                                                            | 11 |

| 3.1 Attack types                                                              | 11 |

| 3.1.1 Focused attack                                                          | 11 |

| 3.1.2 Cryptanalytic attacks                                                   | 12 |

| 3.1.3 Network attacks                                                         | 14 |

| 3.2 Classification of attackers                                               | 16 |

| 3.3 Levels of difficult                                                       | 17 |

| 3.4 Attack vectors                                                            | 17 |

| 4 CLASSIFIYING VULNERABILITIES                                                | 18 |

| 4.1 Classification by SDLC (Software Development Lifecycle)                   | 18 |

| 4.2 Classification by attackers objective                                     | 19 |

| 4.3 Classification by attacks by their location in OSI model and their origin | 19 |

| 4.4 Classification by effected technology                                     | 20 |

| 4.5 Classification by errors                                                  | 20 |

| 4.6 Classification by enabled attack scenario                                 | 20 |

| 4.7 CLASP Classification                                                      | 21 |

| 4.8 Range and type errors                                                     | 21 |

| 4.9 Environmental errors                                                      | 21 |

| 4.10 Synchronization and timing errors                                        | 21 |

| 4.11 Protocol Errors (46.)                                                    | 22 |

| 4.12 Generic Errors                                                           | 22 |

| 4.13 Popular Dictionaries for Attack Taxonomy                 | 23 |

|---------------------------------------------------------------|----|

| 4.13.1 PLOVER                                                 | 23 |

| 4.13.2 CWE                                                    | 23 |

| 4.13.3 CAPEC                                                  | 24 |

| 5 PRINCIPLES OF SECURITY                                      | 26 |

| 5.1 Confidentiality                                           | 26 |

| 5.2 Integrity                                                 | 27 |

| 5.3 Availability                                              | 27 |

| 6 DESIGN CHALLENGES                                           | 29 |

| 6.1 Resource limitations                                      | 29 |

| 6.2 Reliability                                               | 29 |

| 6.3 Cost constraints                                          | 30 |

| 6.4 Functionality creep                                       | 30 |

| 6.5 Knowledge Gap                                             | 30 |

| 7 MECHANICAL DESIGN ASPECTS                                   | 31 |

| 7.1 Product housing                                           | 31 |

| 7.1.1 External Interfaces                                     | 31 |

| 7.1.2 Anti-tamper mechanisms                                  | 32 |

| 7.2 PCB design and routing                                    | 34 |

| 7.3 Memory and bus protection                                 | 35 |

| 8 HARDWARE ASSISTED SECURITY                                  | 36 |

| 8.1 Smart Card                                                | 36 |

| 8.2 TPM                                                       | 36 |

| 8.2.1 Root of trust for storage management                    | 39 |

| 8.2.2 Root of trust for reporting                             | 39 |

| 8.2.3 Root of trust for measurement                           | 39 |

| 8.3 Secure Element                                            | 39 |

| 8.4 Hardware assisted boot process                            | 40 |

| 8.5 Hardware assisted isolated/trusted execution environments | 42 |

| 9 SECURITY ARCHITECTURES                                      | 46 |

| 9.1 Static root of trust measurement                          | 46 |

| 9.2 Dynamic root of trust for measurement                     | 49 |

| 9.3 Multiple Independent layered security (MILS)    | 49 |

|-----------------------------------------------------|----|

| 9.3.1 Separation kernel (SK)                        | 51 |

| 9.3.2 MILS Device Drivers                           | 52 |

| 9.3.3 Hardware support                              | 53 |

| 9.3.4 Middleware services                           | 53 |

| 9.4 Trusted execution environment (TEE)             | 54 |

| 9.5 Virtualization                                  | 55 |

| 9.6 Platform security                               | 56 |

| 9.6.1 Process Isolation                             | 56 |

| 9.6.2 Access Control permissions                    | 57 |

| 9.6.3 Operating systems support and extensions      | 59 |

| 9.6.4 Integrity management                          | 60 |

| 10 DEVICE SECURITY                                  | 62 |

| 10.1 Isolated Execution Environment                 | 62 |

| 10.2 Protection of Confidential data                | 63 |

| 10.3 Device Identification (via Remote Attestation) | 64 |

| 10.4 Secure provisioning                            | 66 |

| 10.5 Trusted path                                   | 67 |

| 11 CONCLUSION                                       | 70 |

| 12 REFERENCES                                       | 73 |

# VOCABULARY

| AppArmor | A Linux Security Module                                   |  |

|----------|-----------------------------------------------------------|--|

| BYOD     | Bring Your Own Device                                     |  |

| CAPEC    | Common Attack Pattern Enumeration<br>And Classification   |  |

| CVE      | Common Vulnerability Enumeration                          |  |

| CWE      | Common Weakness Enumeration                               |  |

| DoS      | Denial Of Service                                         |  |

| eLibc    | Embedded C library                                        |  |

| Gerrit   | Code collaboration tool                                   |  |

| GIT      | Distributed version control system for development        |  |

| юТ       | Internet of things                                        |  |

| PLOVER   | Primary list of vulnerabilities examples for researchers. |  |

| Меедо    | Linux distribution for mobile devices                     |  |

| MILS     | Multiple Independent Levels Of Secu-<br>rity              |  |

| SDLC     | Software Development Lifecycle                            |  |

| SE       | Secure Element                                            |  |

| SELinux | Security Enhanced Linux                        |

|---------|------------------------------------------------|

| SoC     | System On Chip                                 |

| SK      | Separation Kernel                              |

| Stuxnet | Computer worm that targets Industrial networks |

| SUDO    | Sudo access rights                             |

| TEE     | Trusted Execution Environment                  |

| ТРМ     | Trusted Platform Module                        |

# **1 INTRODUCTION**

Security in embedded systems has been gaining attention every passing day. With the advent of IoT and cloud technologies, security is ubiquitous and has found its way in most of the fields like telecom, aerospace, healthcare, smart, wearable devices and defence. Its presence is set to increase with the upcoming technologies, such as like Cloud, robotics, machine learning and AI, and it has not hit the peak.

Given its importance, security should be treated as an integral part of design which should be considered right from the product conception stage. Security should be built into the system across multiple levels, often referred as a layered approach. It is not feasible or often viable to design a totally fool-proof system. Thus, designers should rather focus on systems that can be difficult to compromise and can reduce the risk to an acceptable level. Amit and Barnum state (1.) that it is much easier to find vulnerabilities in soft-ware than it is to make software secure. This can be applied when designing the product end to end and it is not limited to just software.

# 2 DRIVERS FOR DEVICE SECURITY

In the current IoT (Internet of Things) age, it is possible to we pretty much can assume that almost every entity acts as a connected node in the network. The list includes but is not limited to, mobile phones, surveillance IP cameras, consumer appliances, parking spaces, power plants, cars and mass transportation vehicles. (2.) By the year 2020, analysts estimate that there could be 50 billion Internet connected devices which is only bound to grow. (2.)

This also means that this increasing number of nodes needs to be protected in the network: not only to establish a secure, reliable communication but also run a device without compromising the device's integrity and authenticity. These are the primary non-functional requirements that are targeted to be achieved by the security solutions.

Devices can be compromised either by running unauthorized software or by software being subject to hacking. Compromised devices can result in exposing users or organization secrets, such as cryptographic keys, information stealing and assets loss. This can have wider financial implications. It comprises user privacy and creates a blow to confidentiality. Thus, it is extremely important to have appropriate security solutions that can detect and repel any such attacks, and perform a damage control and an incident response mechanism in the event of any such attacks.

# **3 SECURITY ATTACKS**

The formal attack terminology widely used by industry consists of attack trees, attack windows and patterns that are used to describe any attacks.

Attacks can be classified based on certain parameters, such as attacker's objectives, impacts, Origin, phase of introduction, technology employed and exploitability. The purpose of any attacks is to achieve a desired goal that can range from data stealing, inflicting serious damage and crippling the system, hobby attacks and academic or institutional attacks as part of research to expose vulnerabilities. In the attack terminology, the purpose of an attack is viewed as a root. And by initiating an attack, attacker's target is to reach the root of the attack tree.

Attack trees also provide a formal and methodical way of describing the security of systems based on varying attacks. (3.) In an attack tree with only "or" branches, this consists of all paths from a leaf node to the root node. Such paths are also known as "attack paths." In a tree with some "and" branches, an attack pattern may be a sub-tree of the attack tree that includes the root node and at least one leaf node. (1.) Attack patterns provide a coherent way of teaching designers how their systems may be attacked and how they can effectively defend them. (3.) Different attack types are described below in detail

#### 3.1 Attack types

#### 3.1.1 Focused attack

Focused attacks are highly focused on particular or specific kinds of systems or environments or ecosystems. This kind of attack has no limitation on time, money and resources. The most practical examples of these kinds of attacks are to targeting to defence installations and penetrating enemy communication lines. The most recent example of this kind of attack is building of "stuxnet" which is targeted to attack at only Siemens systems in Iran.

#### 3.1.2 Cryptanalytic attacks

Cryptanalytic is a study of techniques to unravel the meaning of an encrypted text without access to secret keys. Cryptanalysis techniques are used to decrypt the ciphered text without really accessing the encryption keys. Doing a cryptanalysis requires working knowledge of the system and knowing the internals of cryptography which in practice means uncovering the secret key. These attacks are briefly classified as plain and cipher text attacks and are explained below.

#### Known plain text attack

In this kind of attack, the attacker will have access to at least one pair of a plain text and corresponding cipher text which are not explicitly chosen and act as inputs for further analysis. (43.) These plain texts are usually obtained via eavesdropping or from parities who already possess the encryption key. The results are used to break the rest of the encryption in the system by tracing out the secret key.

#### Chosen plain text attack

A chosen-plaintext attack (CPA) is an attack model for a cryptanalysis which presumes that the attacker can obtain the cipher texts for arbitrary plaintexts. (4.) In this kind of attack, the attacker feeds a pre-chosen text into the cipher oracle after which they analyse the result and in the worst case they can find the secret key.

Two forms of chosen plain text attacks are a batch chosen plain text attack and an adaptive plain text attack. The batch chosen plain text chooses all the plain texts before it analyses the ciphered text where as in the adaptive chosen text attack, a cryptanalyst requests for additional cipher texts after analysing the results of previous cipher operations.

#### Known cipher text attacks

Under known cipher text attacks also referred as Ciphertext only attack (COA), the attacker has access to bunch of cipher texts mostly obtained either by eavesdropping or stealing. Also here the attacker will not have access to more cipher texts or will not have the luxury of choosing a cipher text or producing more. In this attack, attacker has access only to the encrypted message, as the language is known a frequency analysis could be attempted. In this situation the attacker does not know anything about the contents of the message, and must work from ciphertext only. (44.) This is certainly one of the weakest attacks as the attacker will have nothing to work against other than a few cipher texts in hand.

#### Chosen cipher text attacks (CCA)

A chosen cipher text attack is a scenario in which the attacker has the ability to choose cipher texts and to view their corresponding decryption's plaintext. (5.) In this kind of attack, the attacker selects the cipher text, sends it to the victim, and is given in return the corresponding plaintext or some part thereof. (6.)

It is essentially the same scenario as a chosen plaintext attack but it is applied to a decryption function instead of the encryption function, which means that the attacker will be able to produce a clear text from a set of pre-selected ciphered text messages from the decryption oracle.

Chosen cipher text attacks can be adaptive or non-adaptive. Under non adaptive cipher text attacks, the attacker chooses certain cipher texts in advance for decrypting them. The clear texts obtained are not used for the next cipher operations. A chosen-plaintext attack is called adaptive if the attacker can choose the cipher texts depending on the previous outcomes of the attack. (6.) Servers using the Cipher Block Chaining (CBC) mode of operation and RSA PKCS1 are under certain circumstances vulnerable to adaptive chosen-cipher text attacks and such attacks allow an attacker to recover the encrypted data. (7.) This means that adaptive cipher text attacks are more context based and a result of outcome of previous operations. These attacks may be quite practical in the public-key setting. Bleichenbacher (8.) demonstrated that a plain RSA is vulnerable to a chosen cipher text attack and some implementations of RSA may also be vulnerable to an adaptive chosen cipher text attack. The chances of finding the secret key with chosen cipher-text attacks is more than simple plain text attack.

## Lunchtime Attack

Lunchtime attacks are also referred to as a midnight attack or a CCA1 attack. This kind of attack is targeted by attackers when the owner or user of the system is away or often when the system is not logged in. The idea is that the system is vulnerable and there is often less or no resistance when there is no active user who otherwise would be more challenging to penetrate. During this time, the attacker will generate pre-chosen cipher text quarries which are valid until the period of time after which penetrating will be difficult.

## Adaptive cipher text attack

An adaptive cipher text attack is also referred as a CCA2 attack and it is stronger in nature compared to CCA1. This attack relies on selecting a cipher dynamically at runtime whenever the attacker is posed of challenge.

This is an interactive based attack where the attacker sends a stream of ciphered texts to be decrypted and subsequent ciphered texts are chosen depending on the responses from the system (7.).

In an increasing order from weakness to strength, the above attacks can be sorted as a known cipher text attack, a known plain text attack, a chosen plain text attack and a chosen cipher text attack.

## 3.1.3 Network attacks

In this world of ever increasing networking, systems have become very attractive targets for external attacks through the network. Networking attacks mostly rely on monitoring, spoofing or masquerading of network traffic.

## Passive attacks

A passive attack monitors the unprotected or weekly encrypted communication between two nodes for capturing authentication information or passwords which can be passed to parties who would or have the ability to compromise the system.

#### Active attacks

Active attackers penetrate the system by circumventing the security and breaking the protection of existing systems. They can cause undesired effects by executing their malicious code and injecting viruses or Trojan horses. Active attacks can have varied effects right from minor ones to bringing down the whole system or network especially if the attack is on servers.

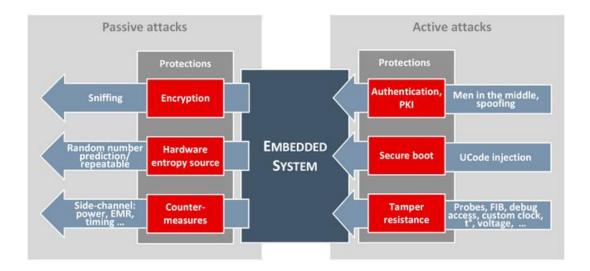

FIGURE 1. Example of attacks on embedded systems (11.)

## **Insider attack**

These are the attacks that are perpetrated from inside the organization or persons who have genuine access to the system. Insider attacks come from disloyal persons, persons with malicious intent or dissatisfied employees inside from an organization.

#### Phishing attack

Phishing attacks are attacks where the attacker will design fake almost identical web sites through which they direct users to login with credentials. These credentials will be recorded and used by attackers to log into proper websites

which can result in stealing of vital information or can even result in financial frauds if the target is banking sites.

# Hijack and spoof attacks

An IP spoofing attack is one in which the source IP address of a packet is forged. There are generally two types of spoofing attacks: IP spoofing used in DoS attacks and man in the middle attacks (9.).

The attacker can hijack the communication sessions and disconnect the one of the node. Under a hijacked session, other connected party is still under the impression that they are communicating with the original party and can still pass some vital private or secret information.

# 3.2 Classification of attackers

# **Class1: Clever Outsiders**

Outsiders are external attackers exploiting a certain weakness in the system, they have certain knowledge of the system.

# Class2: Knowledgeable insiders

Insider attackers are the ones who have the needed technical expertise as well as access to specialized tools to break into the system.

# **Class3: Funded Organizations**

Organizations fund attacks with focused objectives. Here, attackers have indepth knowledge and no restriction on funding. They are also equipped with highly specialized tools to break open the systems.

TABLE 1: Classification of attacks calibrated against different parameters, demonstrated in black hat conference by Joe Grand (10.).

| Resource | Hacker class | Academic  | Organized | Government |

|----------|--------------|-----------|-----------|------------|

|          | (Class1)     | (Class 2) | (Class 3) | (Class 4)  |

| Time     | Limited      | Moderate  | Large     | Large      |

| Budget        | < \$1000  | \$10K – \$100k | >\$100k | Unknown |

|---------------|-----------|----------------|---------|---------|

| Creativity    | Varies    | High           | Varies  | Varies  |

| Detectability | High      | High           | Low     | Low     |

| Target        | Challenge | Publicity      | Money   | Varies  |

| Number        | Many      | Moderate       | Few     | Unknown |

| Organized     | No        | No             | Yes     | Yes     |

| Release Info  | Yes       | Yes            | Varies  | No      |

## 3.3 Levels of difficult

TABLE 2. Attack difficulty (10.)

| Level | Name          | Description                    |

|-------|---------------|--------------------------------|

| 1     | None          | Primitive ,No special tools or |

|       |               | skills needed                  |

| 2     | Intent        | Minimal skills needed to       |

|       |               | compromise the system          |

| 3     | Common tools  | Technically competent, Can     |

|       |               | be dealt with tools available  |

|       |               | in the market                  |

| 4     | Unusual tools | Can be compromised with        |

|       |               | tools, is available to most    |

|       |               | people                         |

| 5     | Special tools | With specialized tools and     |

|       |               | with expertize only available  |

|       |               | in universities or government  |

| 6     | In Laboratory | Major effort needed, Only      |

|       |               | available to few facilities in |

|       |               | the world.                     |

## 3.4 Attack vectors

Attack vectors are typical routes via which an attacker can gain access and after that exploit the vulnerabilities in the system in order to achieve their objective. Typical attack vectors are eves dropping, brute force attacks, injecting crafted packets, reverse engineering and fabrication by counterfeit assets of a product.

# **4 CLASSIFIYING VULNERABILITIES**

According to the CVE website, a vulnerability is a mistake in software code that provides an attacker with direct access to a system or network. For example, the vulnerability may allow an attacker to pose as a super user or system administrator to gain full access privileges. (12.)

An exposure, on the other hand, is defined as a mistake in software code or configuration that provides an attacker with indirect access to a system or network. (12.) Classification of attacks and vulnerabilities can help to understand the tools, remedies and approaches that can help us to contain, trace and overcome these vulnerabilities.

## 4.1 Classification by SDLC (Software Development Lifecycle)

Vulnerabilities can be classified based on the phase of the software development life-cycle they usually appear. Some of the popular lifecycle phases that a have higher chance to see system vulnerabilities are design, testing, deployment and maintenance phases. (45.)

Typical examples of vulnerabilities in a design phase can include a wrong choice of OSS components, protocol and algorithms, using of untested reusable libraries or code that may not be really a fool proof. Often vulnerabilities in design phases are easy to exploit and difficult to plug.

During a maintenance phase, systems can be prone to vulnerabilities that come along with improper bug fixes and components that are not updated on timely and priority basis. In case the system is using OSS or reusable closed sources, system integrators need to update the system with the latest fixes from upstream. Leaving them unmaintained can expose holes in the system makes the system an attractive target for exploit. Vulnerabilities that appear due to coding errors, relaxed compiler settings and bad design of APIs are few that evolve during the implementation phase. Some of these can be addressed by employing a stricter process approach towards using code analysis tools and fine tuning the compiler optimization options.

In a typical software development life-cycle, system shall be configured to relax certain hard rules to accommodate testing and debugging. Eventually, If these are not closed can act as potential attack points. E.g. opening debug ports, opening access points in hardware.

## 4.2 Classification by attackers objective

One of the most prominent approaches is to enumerate the attacks by attackers objectives, such as gaining root access and higher privileges, creating a denial of service, stealing confidential and sensitive data, executing malicious code and Integrity and security policy violation.

## 4.3 Classification by attacks by their location in OSI model and their origin

One approach of classifying the vulnerabilities is by deciding where exactly they appear in the 7 layered OSI reference model. In practice this means segregating the vulnerability into one of the seven baskets (application, presentation, session, network, link and physical layer). Attacks can also be enumerated depending on their original location in the network, such as a local system, intranet (Ethernet network), an internet, particular protocol (e.g. TCP/IP) and a wireless network. ( 46.)

Mitigations for addressing these exploits can be implemented on different objects at different layers in OSI model. A mitigation may be applied at the source code level that eliminates a security flaw and the associated vulnerability, or a work-around can be applied at a system or network level to prevent the security flaw from being exploited. (47.) But this kind of classification may not be appropriate at all times as many of the times vulnerabilities can fall between layers and hence, it is difficult to segregate on this layered approach. For example, it is

not often easy to decide on whether the vulnerability is exactly in the OS in the application layer or both as contention results which is right and wrong.

# 4.4 Classification by effected technology

Systems get vulnerable though holes created by string exploits and buffer overflows which are not unusual in the C language. (47.) Likewise, systems can be prone to attacks that exploit meta characters vulnerabilities in the LDAP and SQL Injection with database languages.

Systems that run code with memory leaks and malicious code are vulnerable to a resource exhaustion and thus can block the system resources resulting in DoS attacks. This kind of technology classification may not suit for vulnerabilities that spawn across technologies, not just limited to one.

# 4.5 Classification by errors

System can be made vulnerable as a result of improper code design and programmatic errors that appear and during the implementation phase. A few of them are freeing the memory more than once and executing code from malicious memory locations or locations program either did not allocate or have any control on.

At times, unclosed holes that are left in production code to accommodate debugging for diagnostic purposes can spell trouble and can be exploited by attackers. (47.)

# 4.6 Classification by enabled attack scenario

Vulnerabilities can also be classified based on precise type of attack scenarios. As seen above, Denial of Service is an effect that can happen due to multiple reasons, such as memory leaks or buffer overflows. Thus, it is sensible to classify the vulnerabilities on the nature of an attack scenario rather than based on effects. Examples of attack scenarios are cryptographic attacks, network attacks, secure storage attacks, Software attacks, entropy attacks and malicious code execution. Techniques employed to execute these attacks can be chosen-known/cipher text attacks, compromised boot sequence and string exploits.

#### 4.7 CLASP Classification

CLASP (Comprehensive light weight application security process) enumerates vulnerabilities based on software events and conditions that are responsible for the vulnerability. (13.)

#### 4.8 Range and type errors

Generic range type errors are errors due to buffer overflow, stack and heap overflow, integer overflow, truncation errors, signed and unsigned errors, integer coercion errors, unchecked indexing of arrays, NULL character misplacing for string buffers, NULL pointer dereferencing, usage of freed memory, format string and code injection into data areas of memory. (47.)

#### 4.9 Environmental errors

The vulnerabilities can be classified based on environment condition in which the application is deployed. The same program image can have different properties when installed in different environments (for e.g. as a result of dynamic runtime linkage). (47.) Environmental errors could also occur due to resources exhaustion (e.g. sockets, kernel objects, file descriptors, memory), execution of untrusted code and data, system variable manipulations (e.g. system paths, library paths), spoofing of system events, a failure to protect secure data and keys, a TRNG generation failure and insufficient entropy for PRNG.

#### 4.10 Synchronization and timing errors

Situations leading to synchronization and timing errors are race conditions in code (unlocking code via kernel objects), race condition in signal handlers, improper references for symbolic names which change at runtime, failure to drop

user privileges at right times soon after task is accomplished, leaking sensitive information through error messages, time to check and time to use errors (for example, resources can change their state between a window of time lag between their validation and actual usage). Potential race conditions in the design could also bring up new vulnerabilities that attackers tend to exploit. At an even higher level of abstraction, these vulnerabilities could be classified as a logic or design error, since a resource (in this case, the file or socket) can be deleted while in use. (47.) Seacord & Householder in his work (47.) stated that, the lowest level of abstraction this vulnerability could be classified as an input validation problem, since the programmer fails to ensure that the object being validated is the same object the (potentially) insecure operation is performed on.

## 4.11 Protocol Errors (46.)

Protocols errors are the ones that usually arise out of protocol, algorithm errors that are as a result of improper use or wrong choices. (46.) Such vulnerabilities are from failure to check for certification expiration and revocation, key exchange without proper authentication, failure to encrypt communication, failure to do integrity check where ever needed, usage of hardcoded and stored passwords or keys, trusting certain IP address or range of IPs that can be spoofed easily, using of broken, week or risker cryptographic algorithms, improper usage of OSS components and failure to protect confidential and sensitive data.

### 4.12 Generic Errors

Errors that are enumerated based on their generic nature are improper error and exception handling, improper break and jump instructions in code, ignoring return values from functions ,uninitialized variables, failure to free unused resources and memory and unintentional assignment when comparison two values etc. (.47)

# 4.13 Popular Dictionaries for Attack Taxonomy

MITRE is a government funded non-profit organization which publishes and controls standards to be used by community. Below are the popular dictionaries of publicly known information security vulnerabilities and exposures maintained by MITRE. (14.)

## 4.13.1 PLOVER

PLOVER is a primary list of working examples intended for researchers. It lists over 1,400 real world vulnerabilities by their CVE IDs organised as a conceptual framework. This framework offers a platform for discussion for a further analysis and describing them in a further detailed manner. PLOVER is targeted at those who are engaged in analysing vulnerabilities to understand and communicate them in a more abstract level. (14.)

## CVE

CVE stands for Common Venerability Enumeration, which precisely describes a certain pin-pointed instance in a system or a vendor through which exploits can happen. For example, CVE-2015-7547, points to a specific venerable instance in eglibc for an attack.

## 4.13.2 CWE

CWE stands for Common Weakness Enumeration, which essentially deals with underlying software weakness in general but not specific to a particular instance in a system. Vulnerabilities can emerge from weakness and they may have potential for getting targeted. The goal of CWE is to educate the programmers or system designers to For example, CWE-367 is time to check and time to use weakness spotted in software but it is not limited to any specific component or instance in any system.

#### 4.13.3 CAPEC

To respond to attacks effectively, the community needs to think outside of the box and have a firm grasp of the attacker's perspective and the approaches used to exploit software systems. (15.) CAPEC provides this information to the community in order to help to enhance security throughout the software development lifecycle and to support the needs of developers, testers, and educators. (15.) Therefore, CAPEC is a publicly available catalogue of attack patterns along with a comprehensive schema and classification taxonomy created to assist in the building of secure software. (15.) While CWE is a list of software weakness types, Common Attack Pattern Enumeration and Classification (CAPEC<sup>™</sup>) is a list of the most common methods attackers use to exploit vulnerabilities resulting from CWEs. Used together, CWE and CAPEC provide understanding and guidance to software development personnel of all levels as to where and how their software is likely to be attacked, thereby equipping them with the information they need to help them build more secure software.

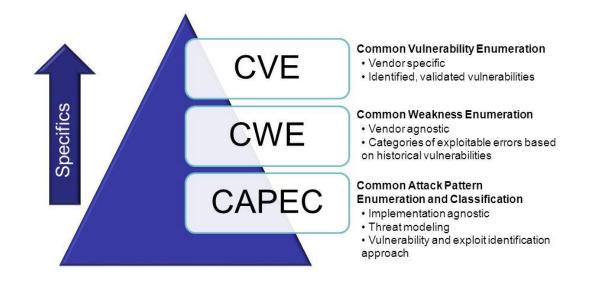

Below is the pyramid described by Knowledge Consulting group (16.) on how CWE- CVE- CAPEC stack each other.

# Relationships

8

FIGURE 2. Relationship between CWE, CVE, CAPEC (16)

# **5 PRINCIPLES OF SECURITY**

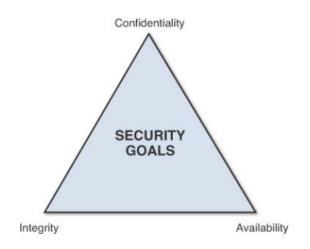

Primary principles of security is to preserve the confidentiality, integrity and availability of the consumers, stakeholders and devices in the operating ecosystem.

"The principle of information security protection of confidentiality, integrity, and availability cannot be overemphasized: This is central to all studies and practices in IS. You'll often see the term CIA triad to illustrate the overall goals for IS throughout the research, guidance, and practices you encounter."—Three goals of security by Jim Breithaupt & Mark S. Merkow are shown in figure 3.

FIGURE 3. CIA Triad (17.)

### 5.1 Confidentiality

Confidentially refers to a restriction of access to sensitive data from unauthorized people. Loss of sensitive information, such as device or user passwords, credit card and banking credentials could result in identity theft, financial implications and compromised privacy.

According to Mathew and Stan (18.), designers should strongly consider measures to ensure confidentiality and prevent sensitive information from reaching unauthorized people, while simultaneously making sure that the right people can in fact get it: Access must be restricted only to those authorized to use the data in question. It is common, as well, for data to be categorized according to the amount and type of damage that could be done should it fall into unintended hands. (18.)

## 5.2 Integrity

According to study published in a security blog by Mathew and Stan (18.), integrity involves maintaining the consistency, accuracy, and trustworthiness of data over its entire life cycle. Data generated at a source must not be changed in transit, and steps must be taken to ensure that data cannot be altered by unauthorized people (for example, in a breach of confidentiality). For ensuring data integrity designers can employ the measures like, consider file permissions, user access controls, employing cryptographic checksums for verification. Also, designers need to plan for backups in the event of any damage to data to restore it to its correct state. (18.)

## 5.3 Availability

Terry refers to availability as one of the pillars in the CIA traid (19.), According to a report published by her, availability of information refers to ensuring that authorized parties are able to access the information when needed. This can also be applied just not only to information, but also to systems that cater services. DoS attacks on such systems will deprive and deny users to access systems, thus hurting the systems availability. If critical services (systems) are attacked and brought down, it could cripple services and caste impact on economy and people's lives. DoS attacks on mission critical systems such as aircraft and space ships can hurt the availability and can bring down the whole system threating the lives.

Terry (19) advocates the importance of taking regular backups to ensure the data availability in the event of any natural disasters. Redundancy might be a solution for information services that are highly critical. These redundant copies

can be stored in different geographical areas to mitigate against natural disasters and intentional attacks by mala fide people. Designers, while designing embedded products should ensure that the systems can repel or filter such Dos attacks, have proper intrusion detections mechanisms, can raise an alarm, have damage control mechanisms in place in the event of any such attacks.

Extra security equipment or software such as firewalls and proxy servers, can guard against downtime and unreachable data due to malicious actions, such as denial-of-service (DoS) attacks and network intrusions. (19.)

|                                                                                                                                                                                                                             | POTENTIAL IMPACT                                                                                                                                                                                                               |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Security Objective                                                                                                                                                                                                          | LOW                                                                                                                                                                                                                            | MODERATE                                                                                                                                                                                                                       | HIGH                                                                                                                                                                                                                                             |

| <b>Confidentiality</b><br>Preserving authorized<br>restrictions on information<br>access and disclosure,<br>including means for<br>protecting personal<br>privacy and proprietary<br>information.<br>[44 U.S.C., SEC. 3542] | The unauthorized<br>disclosure of information<br>could be expected to have<br>a <b>limited</b> adverse effect on<br>organizational operations,<br>organizational assets, or<br>individuals.                                    | The unauthorized<br>disclosure of information<br>could be expected to have<br>a <b>serious</b> adverse effect on<br>organizational operations,<br>organizational assets, or<br>individuals.                                    | The unauthorized<br>disclosure of information<br>could be expected to have<br>a <b>severe or catastrophic</b><br>adverse effect on<br>organizational operations,<br>organizational assets, or<br>individuals.                                    |

| Integrity<br>Guarding against improper<br>information modification<br>or destruction, and<br>includes ensuring<br>information non-<br>repudiation and<br>authenticity.<br>[44 U.S.C., SEC. 3542]                            | The unauthorized<br>modification or<br>destruction of information<br>could be expected to have<br>a <b>limited</b> adverse effect on<br>organizational operations,<br>organizational assets, or<br>individuals.                | The unauthorized<br>modification or<br>destruction of information<br>could be expected to have<br>a <b>serious</b> adverse effect on<br>organizational operations,<br>organizational assets, or<br>individuals.                | The unauthorized<br>modification or<br>destruction of information<br>could be expected to have<br>a severe or catastrophic<br>adverse effect on<br>organizational operations,<br>organizational assets, or<br>individuals.                       |

| Availability<br>Ensuring timely and<br>reliable access to and use<br>of information.<br>[44 U.S.C., SEC. 3542]                                                                                                              | The disruption of access to<br>or use of information or an<br>information system could<br>be expected to have a<br><b>limited</b> adverse effect on<br>organizational operations,<br>organizational assets, or<br>individuals. | The disruption of access to<br>or use of information or an<br>information system could<br>be expected to have a<br><b>serious</b> adverse effect on<br>organizational operations,<br>organizational assets, or<br>individuals. | The disruption of access to<br>or use of information or an<br>information system could<br>be expected to have a<br><b>severe or catastrophic</b><br>adverse effect on<br>organizational operations,<br>organizational assets, or<br>individuals. |

FIGURE 4. Potential Impacts for CIA (20.)

# **6 DESIGN CHALLENGES**

#### 6.1 Resource limitations

Embedded software has traditionally evolved as "software on devices with limited resources". In this traditional view, the principal problem is resource limitations (small memory, small data word sizes, and relatively slow clocks). (21.) Given their size, portability and cost sensitiveness, they also often come with other resource limitations, such as computational power, absence of protective theft and shielding technologies when compared with a larger system. Among the examples, the Mission Critical system has much more stringent size and weight requirements than the others because of its use in a flight vehicle. (22.) For consumer devices, such as mobile phones and IoT devices, apart from size and computational power limitations, it is extremely important for these kinds of devices to be designed keeping the security of the user data and software attacks in mind.

While designing embedded systems, designers have to work with those above mentioned design challenges and at the same time they have to ensure users' integrity of data and secrets, and damage limitation in case a system or a device is compromised due to a multitude of reasons.

#### 6.2 Reliability

Embedded software systems are generally held to a much higher reliability standard than any general purpose software. (21.) They are also known to work in extreme and tough conditions, therefore they are prone to more failures. Sometimes these the failures associated with embedded systems can be quite risky and threating. They can cause substantial damage in terms of monitory or personal loss. In mission-critical applications, such as an aircraft flight control, a severe personal injury or an equipment damage could result from a failure of the embedded computer. (22.) A failure to safeguard the user data in a mobile phone can have financial implications. Traditionally, such systems have employed multiply-redundant computers or distributed consensus protocols in order to ensure a continued operation after an equipment failure. (22.) Thus, it is important that, designers create alternate solutions for mission critical systems. But IoT devices designers should consider damage limiting functionalities for consumers in case of any software attack or physical tampering.

## 6.3 Cost constraints

Most consumer segment devices are designed keeping the cost factor in mind. Achieving a reliable system under controlled costs can be challenging for system designers. While designing cost consensus devices, designers keep the overall system costs controlled by keeping system complexity down, which should not affect the integrity or reliability of the overall system.

## 6.4 Functionality creep

Designers tend to improve the functionality of the products to compete in the market with their competitors. This is partly because consumers prefer to choose products offering the better functionality against the ones that offer more secure solutions. Therfore, in this ball game, it is often challenging for designers to balance the security features with the functionalities.

## 6.5 Knowledge Gap

A challenge in the area of designing secure solutions arises from the fact that attackers have been learning how to exploit the products for several decades, but the general solution designers have not kept up with the knowledge that attackers have gained. (3.) Therefore, it will be challenging for designers to get ahead of the attackers to come up with good solution.

# 7 MECHANICAL DESIGN ASPECTS

This chapter introduces mechanical design approaches that should be considered to bring out a secure product.

# 7.1 Product housing

A typical attack hard point in this case would be a product enclosure and an attack vector where attackers will make an effort to open the casings and access to internal circuitry and components. Product designers need to prevent an easy access to the product internals by concealing the access points through which the device can be opened.

Some of the safe enclosure techniques currently in use are

- designing a product with a single piece outer shell.

- using high melting point glues wherever needed.

- designing in such a way that the opening of a device needs a complete destruction.

- in addition to the above mentioned, leaving the surface points of device accessibility for service personnel who can open the device with specialized tools.

# 7.1.1 External Interfaces

External interfaces, such as proprietary connectors, Ethernet, RS232, USB, Firewall, JTAG, Wireless (802.11) and Bluetooth are a vital lifeline for the product to the outside world so that the device functions properly. In addition to carrying the usual device operations, these interfaces also aid in regular maintenance tasks, on-field diagnostic procedures and field programming.

External interfaces are always attractive targets for hackers as the root of the attack tree can originate from here. Attackers indulge in probing, sniffing, flood-ing and pushing malformed packets through these interfaces. Product designers

should be able to defeat all possible attacks that originate from these external interfaces. Designers should remember the below mentioned issues while they are designing interfaces.

- A device must transmit only non-sensitive and public information in clear text format.

- All sensitive and confidential information that has to be exchanged over interfaces, must be encrypted.

- Adequate protection must be added inside the device to defeat spoofing, malformed packets. e.g, hardening of OS, strong firewall.

- Strict no obfuscation policy. Attackers are always ahead of designers and can uncover them easily.

- All the diagnostic ports, backdoor interfaces and JTAG connectors must be removed from production software images. Closing them by employing techniques, such as blowing resisters and fuses, is not the best approach as they can be reopened by attackers.

## 7.1.2 Anti-tamper mechanisms

Attackers try to gain physical access to a device by tampering to know confidential information and working internals device. Some of the tamper mechanisms worth considering by product designers are described below:

#### **Tamper resistance**

Tamper resistance relies on restricting physical access to devices. Devices must shall be housed and constructed with specialized tamper resistance materials and mechanisms, such as hardened steel enclosures, a usage of one way screws and epoxy coating materials, tight airflow channels, a usage of security bits, encapsulating the circuit and critical components to prevent intentional probing and tampering due to environment hazards.

Products with a well-protected housing would require a partial if not a complete destruction of device to open up. It is also essential for designers to lay emphasis on such a design that will leave a visible and clear evidence if a tamper attempt is made.

#### **Tamper evidence**

Tamper evidence mechanisms are designed to ensure that a visible evidence or trails are left of an attempted break in. These mechanisms do not protect the device or the confidential data in it but they raise awareness that there has been an attack on the system. Some of the widely used mechanisms are brittle packages, crazed aluminum and polished packages, bleeding paints and holographic tapes. All the above mentioned mechanisms will leave damages on the surface which would be hard to be unnoticed.

#### **Tamper detection**

Tamper detection can be done by installing relevant sensors which detect the tamper and trigger the relevant response mechanisms. Some of the widely used tamper detection mechanisms that are built into devices are quoted below (23.)

- Switches that detect a mechanical movement.

- Sensors that can detect and inform external environmental changes.

- Closed circuits and cables that are wrapped in and around the device for detecting an attempted break, tamper or modification.

- Monitoring of for the changes in voltages and clock frequencies from and to the chips.

#### Tamper response

Systems should trigger shutdown and disable themselves in response to tamper detection. They should be designed with a capability to log and generate forensic data for a further analysis of post tamper detection that can be accessed by service personnel. Designers should also consider techniques, such as erasing the sensitive data, in response to tamper detection. In products, which houses confidential data, keys should protect the data by resorting to erasing methods.

Confidential data is either stored in RAM or ROM. Erasing the random access memory is relatively easier and it is accomplished by dropping the voltage levels which will effectively clear the memory contents. In case of ROM, a ROM overwrite may be needed. There are even cases where a system employs an ultimate mechanism of physical destruction by shorting the circuits and rendering the device inoperable.

Further, it should be noted that these tamper response mechanisms do not trigger in case of unintentional actions, accidentally or by environmental factors.

## 7.2 PCB design and routing

Enough precautions should be taken while designing circuitry boards for not letting an easy access to components, such as FPGA, processors and memories. An easy access to these components and circuitry can help attackers in reverse engineering the product. Designers should look into advanced chip packaging technologies while they design PCBs, e.g. COB (Chip on Board) packaging, CIB (Chip In Board) packaging and Ball Grid Array packaging. The product should demark or erase all the chip markings either by black topping or using other methods, such as small sandering or etching. A failure to remove the chip markings will leave potential hints to attackers to learn about the chips behavior and their usage by referring their datasheets.

Sensitive components and circuitry lines should be concealed by using Epoxy material around them. Care should be taken during the PCB production not to leave test points visibly open and every attempt should be made to obfuscate the trace paths and critical lines into inner layers of PCB. Even electromagnetic emissions from the product can act as potential attack points which attackers can monitor to determine secret information. Thus, every step needs to be taken to minimize the emissions by installing an appropriate shielding and taking care of unprotected I/O busses from ESDs. Well-designed power lines and grounding can reduce noise levels and emissions. All unused GPIOs should be either disabled or fixed to a predetermined state.

#### 7.3 Memory and bus protection

Designers should be aware that address and control bus lines are prone to probing and traffic is not secure. Designers need to design their systems to perform secure operations either inside SoC or components that will not use the unsecure bus in the system. Memory devices, such as RAM and ROM, are known to be unsecure. Even though systems are designed with a proper tamper detection and response mechanisms, such as a complete wiping out or erasing of data, there is a high chance that traces of data can still be left out. Although the product supports security fuses, boot-block protection mechanisms, these can be bypassed by die-attacks and chip decapping as attackers can reproduce and recreate cryptographic keys or remove security bits. Designers should also take steps to limit the time secure data can be stored in memory. The secure data should be erased if it is no longer needed.

# 8 HARDWARE ASSISTED SECURITY

Devices can be made more secure if security use cases utilize hardware solutions or extensions in conjunction with software rather than just as a software only solution. In the below sections the focus is on the role of hardware based solutions touching associated software functionalities that exploit these specialized hardware wherever needed. Security solutions that utilize an underlying platform and hardware assistance are more effective than purely software based ones.

#### 8.1 Smart Card

A smart card is an embedded integrated circuit card with a CPU, memory, and at least one peripheral interface to communicate with a host device. (24.)

Every component in the smart card is deemed secure, basic in execution with very less computational power. Smart cards also have a higher level of temper resistance because of their size, a complete physical isolation of the trusted area and narrow interfaces .The isolated trusted area plus a higher level of temper resistance enables that the trusted services leveraged by a smart card are very secure, but very limited in scope due to lower computational capabilities. (24.)

#### 8.2 TPM

Trusted platform modules (TPM) are dedicated secure crypto-processors which are designed to secure hardware or software by integrating cryptographic keys into a device. TPM chips are passive and execute commands from the CPU. They by no means will decide or control the execution flow. Generally, there are additional software components operating from the CPU. They that will interact with TPM chips, which would take action upon validating the content from the TPM. Global standards of specification for the TPM are controlled by a Trusted computing group (TCG) alliance formed by HP, Intel, AMD and Microsoft. The objective of the TCG is to develop, define and promote open standards for hardware enabled trust computing and standardize software interfaces across platforms. These specifications aim to provide a platform independent functionality that must be provided by any trusted platform by facilitating a common interface for a secure computing environment. Thus, protecting and securing the platform against hardware and software attacks. There are also criticisms against TPM specifications. They are said to cripple the user rights by moving rights management from software to computing platform hardware.

TPM chips come with an internal hardware logic for RSA encryption and decryption, a random number key generator, a tamper proof non-volatile secure storage and a hash functionality. Although TCG specifications do not mandate the above to be hard wired, chip vendors prefer them as it can be difficult to fulfil the TCG specifications by just implementing these via software.

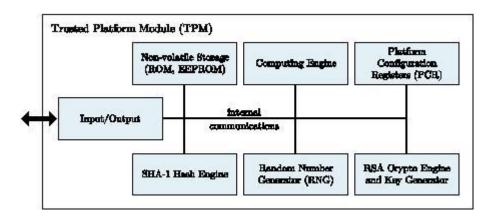

Simplified Architecture of the TPM

FIGURE 5. High-level TPM Architecture (25.)

The first generation chips were physically separate which made the platform less secure. Later on they were either mounted in the mother board or embedded into the SoC. Mounting the TPM chips in the motherboard is prone to physical attacks and it is less secure, too. Mandatory objectives of TPM chips are

- protecting the encryption and public keys from external stealing or getting misused by untrusted components in the system.

- preventing malicious code access to secret keys inside the TPM.

TPM chips achieve the above goals by implementing the functionality listed below

- Authorization: Public key authentication functions that provide on-chip key generation using random number generation hardware, verification, encryption and decryption functionality. Keys inside the TPM can be made to never leave or be visible outside the chip to avoid any kinds of phishing attacks and to prevent the key from being copied and used without the TPM. They can also be configured to be used by providing right authorization values when only they are unsealed. This in practice means that the keys are accessed only when the platform is in a known state.

- Integrity measurement functionality provides the capability to protect the private keys to untrusted code. In a trusted boot scenario, the platform state (hash of configuration) is stored in PCM registers. The private keys are sealed under the specific PCM registers and they get unsealed only if the TPM is provided with the same values by which the integrity of the system is verified. When an attempt is made to boot the system with an unauthenticated image or with a image that has malware or suspicious code built in will result in different PCM values. This kind of boot will fail the integrity check and will render the keys inaccessible.

- Attestation functionality: A mechanism where the TPM can certify the platform as trustworthy and not breached. By using the attestation, trusted clients can prove to the third party that their software is guanine

and not compromised. Attestation functions keep a list of software measurements committed to PCRs and can then carry out a signature using private keys known only by the TPM. During the attestation operation, the evaluating entity will request a TPM quote, which is essentially a signed composite hash of selected PCM data and its signature. The generated TPM quote is compared with the values that are generated during provisioning.

### 8.2.1 Root of trust for storage management

The root of trust for storage is a trusted component that lies inside the TPM that provides integrity and confidentiality checking for secure storage information in the chip. This is achieved using the RSA encryption and integrity checking by validating the platform state to a known value.

### 8.2.2 Root of trust for reporting

The root of trust for reporting is a trusted component that resides inside the TPM and responsible for reporting the platform state and RSA signed data to external parties who ever requests them.

#### 8.2.3 Root of trust for measurement

The RTM (root of trust for measurement) is a piece of code external to the TPM which is responsible for triggering the measurement of platform state. RTM sits inside the core root of trust (CRTM) which is immutable and acts as a root of trust for the measuring environment. This is a small bit of immutable an component that gets executed upon a device reset and which is never changed in its lifetime.

#### 8.3 Secure Element

Secure elements are temper-resistant hardware elements which hold device secrets and a limited isolated execution environment. They can also be added to any device with a micro SD or a Universal Integrated Circuit Card (UICC). (24.) They house cryptographic keys which are not exposed to outside world but would execute crypto operations inside the isolated environment created inside the chip. Evicting the secrets out of the chip for illicit use is either hard or impossible to do.

The main benefits offered by a secure element are

- Data Protection: Protection of data from unauthorized access (24.)

- Hardware assisted cryptographic operations: Dedicated inbuilt hardware logic for cryptographic functionalities, such as encryption, decryption, hashing etc. (24.)

- Isolated execution environment: Small defined tasks (applets) which perform cryptographic operations with keys and data stored inside the SE, can be run in an isolated execution environment without the data leaving the TEE. (24.)

This technology is widely used in the EMV chip on payment cards. Security offered by the SE is considered to be on a greater degree of evaluation level (EVL5) compared to a device that offers solutions over the TEE.

# 8.4 Hardware assisted boot process

As part of a hardware assisted boot process, the boot sofware in the device, which is supposed to be executed to bring up the device at each stage, is verified by a preceeding stage with the help of a hardware mechanism either the TPM or SE. This happens in two phases.

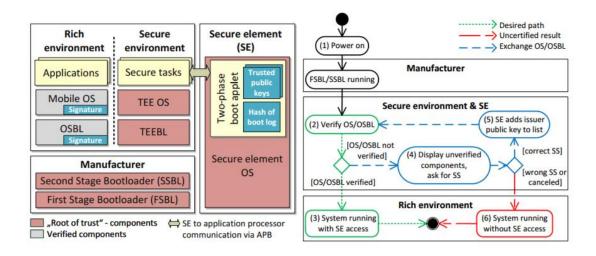

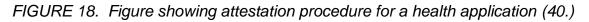

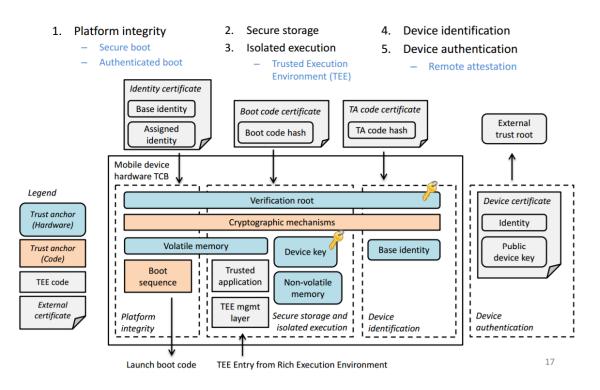

Figure 6 below depicts the interaction between hardware and software components to achieve the two-phase boot verification. As part of a boot process, image signatures of both the traditional OS and its boot loader which is often referred as the normal world are verified by the trusted execution environment (TEE). The trusted execution environment comprises of its TEE boot loader and TEE OS with the SE acting as root of trust. Components that are deemed to be unaltered during the lifecycle and immutable are considered as a root of trust components. They are usually ROM programed in factory and they are bound to never change. On the contrary to the applications running in rich a OS, the secure tasks running in the TEE can be trusted. Also in this case, the SE is configured as a trusted peripheral and it is only accessible from secure tasks that execute in the TEE. In this way, applications running in traditional OSs make use of secure tasks to access the SE. As a consequence, if the TEE becomes unavailable, rich applications would be unable to perform secure use cases, such as device identification, device management, decryption and encryption.

#### FIGURE 6. Architecture of secure execution environment (26.)

The above figure show that the root of trust components considered here are manufacturer's boot loaders and hash of a trusted public key (usually OEMs) in the Secure Element. If not in secure memory, trusted keys can also be stored in hardware one time fuse memory which is only accessible to the secure OS. These OEM keys are fused as part of series of steps in the assembly factory line when the device is manufactured. Under the "hardware assisted secure boot", images that form a chain of verification are pre-signed by the OEMs private key corresponding to the fused public key hash in a secure element or fuse memory. During the secure boot process, manufacturer's bootloder verifies the signed images, which are signed with a corresponding private key, whose hash

of public key is stored in the Secure element. It is purely prerogative of the OEM to consider whether the TEE OS is under the root of trust. In case not, even the TEE OS and its bootloader need to be verified. If the verification at any stage fails, the device assumes to have been tampered and exits the boot phase.

Until now have been discussed the role of secure element or the TEE OS in a secure boot process have been discussed. Alternate solutions also exist, such as using TPMs instead of SEs as shown in figure 7.

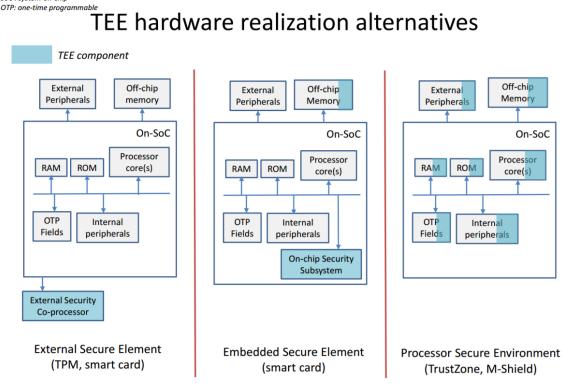

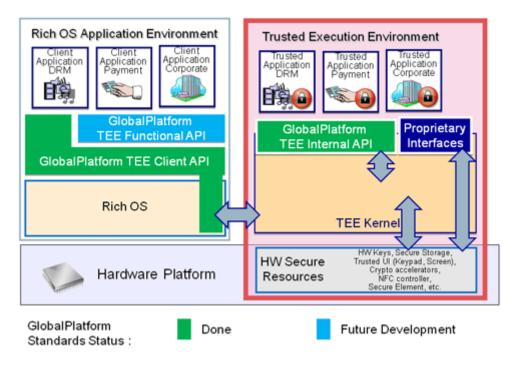

# 8.5 Hardware assisted isolated/trusted execution environments

As described in figure 7, there are more than one way to realize isolation execution environments. Critical applications or part of use cases, which need an isolated execution environment to execute to protect confidentiality and integrity can be executed in these environments.

- External security co-processor can be used for executing sensitive operations and its results can be consumed by the primary processor.

- Using Embedded Secure Elements (ESE), which will be embedded inside the same System On Chip for secure operations.

- Advent of bus and memory isolation hardware extension logic blocks made it possible for a single processor (SoC) to be split into untrusted and trusted execution modes.

Secure peripherals can be accessed only while device is operating in secure mode. Untrusted entities cannot gain access to secure peripherals as they would run only on non-secure mode. Legend: SoC : system-on-chip

Figure adapted from: Global Platform. <u>TEE system architecture</u>. 2011. <sup>19</sup>

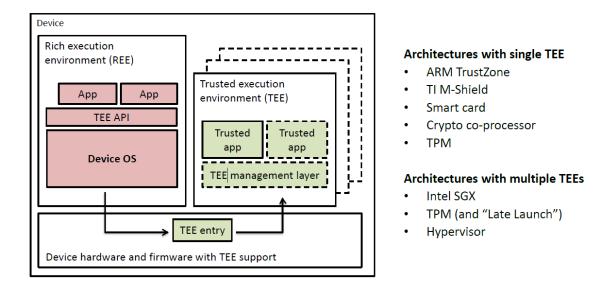

FIGURE 7. TEE Solution Realizations (27.)

Although a secure element offers a higher degree of security, the TEE is gaining momentum in the Industry as it addresses the most of the industry needs for secure applications by offering a higher level of security than any traditional OS, without the constraints associated with the secure element.

Recent trends show that TEE environments are widely used in mobile payments, enterprise applications, such as BYOD, and in content protection and in government electronic ID solutions.

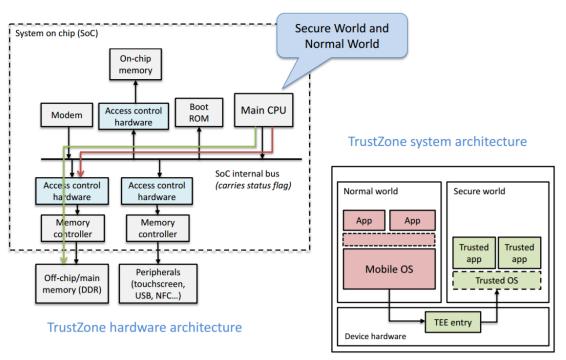

ARM has come out with a trust zone architecture to facilitate the isolated execution environment (often referred as secure mode) against the rich operating systems execution environment (referred as non-secure or normal world mode) by maintaining a hardware separation between these two worlds. The trust zone technology (see figure 8) will ensure that data and operations on the device remains secure, protecting consumer privacy and enabling a range of services, such as mobile banking, payment use-cases and playing multimedia entertainment which is meant for consumers and service providers.

TrustZone is incorporated within the same microprocessor core, enabling the protection of on- and off-chip memory. Since the security elements of the system are designed into the core hardware, security issues surrounding proprietary, non-portable solutions outside the core, are removed.

There is a minimal impact on the core area or performance while trustzone enables developers to build any additional security, for example cryptography, onto the secure hardware foundation.

# ARM TrustZone architecture

FIGURE 8.ARM Trustzone Architecture (27.)

Having introduced by ARM 10 years ago, Trustonic and Xilinx were the first ones to propose frameworks and solutions utilizing these hardware platforms.

This enables the research community (28.) as well as the industry to experiment and develop innovative solutions on it.

# **9 SECURITY ARCHITECTURES**

In this chapter it will be discussed the ways software can be designed to exploit the specialized hardware modules (discussed in the earlier chapter) that lay foundation to secure solutions. This chapter also discusses some profound architectures to design software solutions.

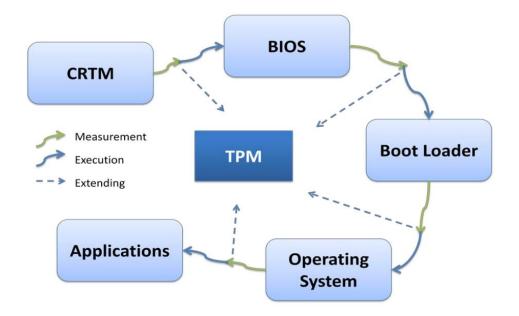

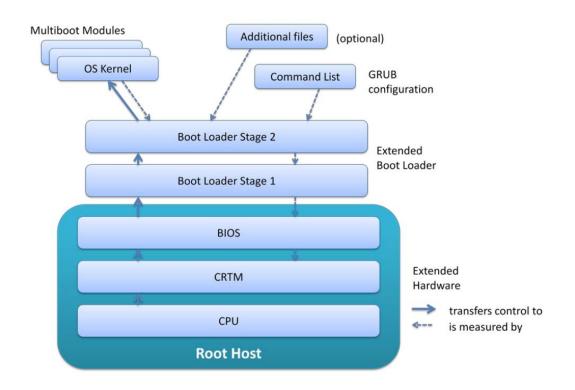

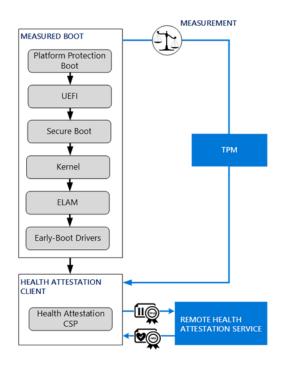

### 9.1 Static root of trust measurement

As implied by name, the static root of trust begins with a piece of immutable code which has not been changed for the lifetime of platform. This piece of code forms the root of trust for the measurement (CRTM). This fundamental entity is referred as a trusted building block (TBB) from where the chair of trust originates.

In any embedded system the first executable is usually the ROM BIOS code, but to enable the static root of trust, there needs to be an additional immutable component, which would verify the bios before it starts to execute, and which is the Core root of trust for measurement (CRTM). The CRTM is either stored in the chip burned in the factory or found in the BIOS as block in the BIOS boot block. All that TCG mandates is to have the CRTM to be present in immutable and it is a true trusted building block.

FIGURE 9. Chain of trust (29.)

The CRTM entity is responsible for measuring the integrity of the next component that follows the boot sequence and for extending the measurement values to predefined Platform Configuration Registers (PCRs). Each of the component that executes will need to verify the next one in the boot sequence and to extend the measurement values to PCRs before transferring the control to the next component

Even though there is not any compromised component in the execution chain, it cannot bypass the chain of trust verification. Also, the comprised components cannot technically extend its measurement values back to PCRs as shown in figure 10 below.

# FIGURE 10. Chain of Trust, Measured boot in use (29.)

Of course, this static method to verify is good for load time, It also comes with few drawbacks, such as scalability and time to check and time to use (TOC-TOU) issues.

Scalability is the issue in case that all the executables, libraries and scripts will need to be part of a verified chain as there is no clear definition for a TCB in all the major operating systems used today. This is partly because all these components are subjected to patching, fixes and a varied order of execution, which can potentially change the PCR measurement values.

The time of measurement plays an important role due to the fact that even though the system can be booted in a known state, it is not guaranteed to be in the same state at the runtime. Potentially, during the execution of code, attackers can look for vulnerabilities and they can put the system to a unsafe state. It is essential to be aware that the Static Root of Trust for Measurement only gives a load-time guarantee not a run-time guarantee, i.e that that is it gives assurance of what program has been loaded, not necessarily what is running. (29.)

### 9.2 Dynamic root of trust for measurement

The above mentioned shortcoming related to the static root of trust has been addressed by the TCG group as part of 1.2 specifications .A dynamic root of trust measurement (DRTM) essentially deals with measuring the system state not just at the boot time but whenever there is a need for verifying the platform arises. The DTRM brings a substantial contribution from hardware side as well. Most semiconductor vendors have introduced special instructions (SKINIT, SENTER for AMD and Intel) which trigger the creation of controlled and attested execution environments in runtime.

The DRTM relies on small trusted piece of code which is loaded from a trusted source whose responsibility is to measure and execute a predefined piece of software. The DRTM comes with a short chain of trust when compared to the static root of trust measurement. This piece of software, which is launched and untainted and not modified right from the device boot time, puts the system into the secure state directly. This in practice means that the device gets into the secure state without a need to reboot or a further need to the static root of trust management.

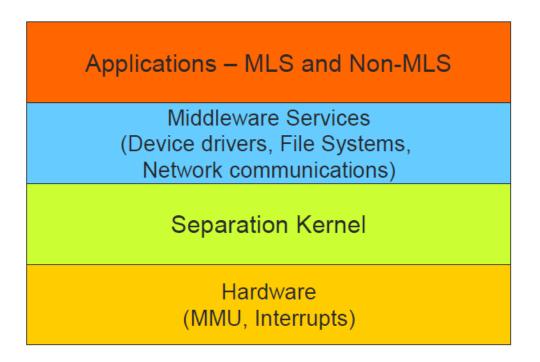

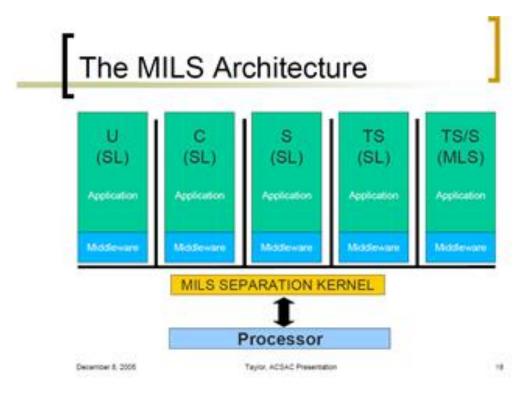

#### 9.3 Multiple Independent layered security (MILS)

Legacy secure systems were designed around a secure kernel and a trusted computing base, with the idea that all the security decisions and the security enforcement mechanisms are an integral part of the TCB. (30.) This methodology can increase the complexity of the TCB as designers tend to add pump in more and more logic there thus creating issues for maintainability.

From the design paradigm, the MILS architecture stands better compared to the legacy one as it forces designers to follow a structured and modular approach.

The Multiple Independent Levels of Security (MILS) is a security architecture based on the concepts of separation and a controlled information flow implemented by the separation mechanisms, which supports both untrusted and trusted code where each level is responsible for its own security domain. Limiting the scope and complexity of the security mechanisms provides users with manageable and, more importantly, evaluable implementations. (31.)

This approach provides applications with mechanisms to control, manage and force their security policies in a manner that enforcement mechanisms are always invoked, mechanisms are non-by-passable, evaluable, and tamperproof. (30.) Under the MILS architecture, privileged mode processing is isolated from under privileged user data or applications. The MILS architecture is targeted at mission critical operations where a failure cannot be even thought of. The MILS architecture is intended to be used at the highest levels of security. Consequently, an EAL 7 will be targeted. (31.)

| Common Criteria                | MSLS / MLS Separation<br>Accreditation   |

|--------------------------------|------------------------------------------|

| Basic Robustness (EAL3)        | System High Closed Environment           |

| Medium Robustness (EAL4+)      | System High Open Environment             |

| High Robustness (EAL6+)        | Multi Level Separation                   |

| DCID 6/3 Protection<br>Level 5 | Multi Nation Separation<br>Accreditation |

| DO-178B Level A                | Failure is Catastrophic                  |

FIGURE 11.Assurance certification goals (32.)

The advantages of the MILS architecture (shown in figure 11 above) are:

Reducing the footprint of secure critical code dramatically, the lesser is better.

- Isolating the critical components and operations in the system.

- One processor can host multiple applications at different security levels.

(31.)

- Certification costs are reduced since individual functions within non-security critical layers can be certified separately. Non-critical functions can be certified at a lower level. (31.)

FIGURE 12. Conceptual VIEW OF MILS layers (33.)

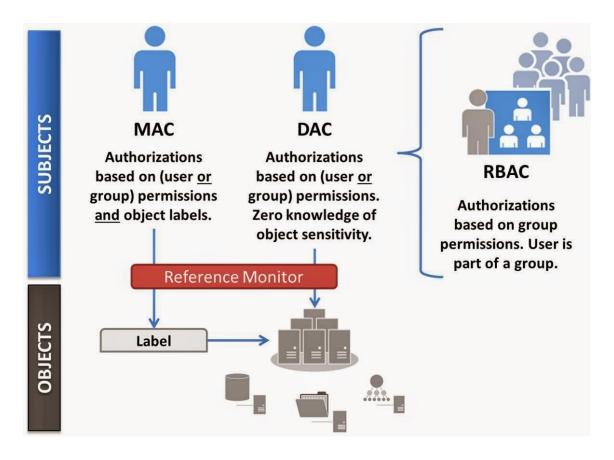

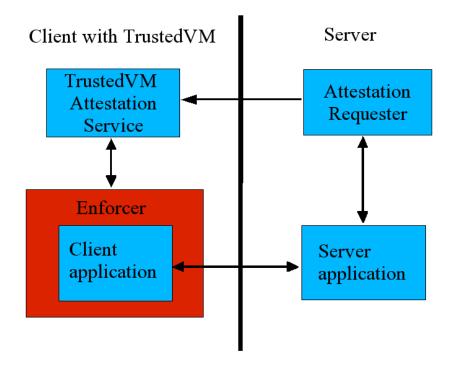

# 9.3.1 Separation kernel (SK)