Expertise and insight for the future

PHUOC TAI VO

# Digital Design and Verification of Adaptive Noise Cancellation Module

Metropolia University of Applied Sciences Bachelor of Engineering Degree Programme in Electronics Engineering Bachelor's Thesis 10 November 2020

| Author<br>Title         | PHUOC TAI VO<br>Digital Design and Verification of Adaptive Noise Cancellation |

|-------------------------|--------------------------------------------------------------------------------|

| Number of Pages<br>Date | 61 pages<br>10 November 2020                                                   |

| Degree                  | Bachelor of Engineering                                                        |

| Degree Programme        | Electronics Engineering                                                        |

| Specialisation option   | Electronics                                                                    |

| Instructor(s)           | Janne Mäntykoski, Senior Lecturer                                              |

Currently, at Metropolia University Applied of Sciences, digital design and implementation based on DSP studies have mainly focused on how to write efficient codes according to common coding styles rule. However, for its verification process before physical design, verification with an HDL testbench is the only method which is instructed in university. Advanced and high-level verification methods, especially UVM, are still not applied for teaching and studies. Apart from that, when it comes to DSP implementation, adaptive filtering approaches were selected to solve the interesting problem of how to track the statistical variations of signal and eliminate random noise over time in a nonstationary environment with massive datasets and unstructured data types for complex hardware implementation. Therefore, the Thesis work aimed to design and implement an adaptive FIR filtering noise cancellation module based on LMS algorithm and verify its functional specifications.

In the Thesis work, an adaptive noise cancellation module was developed to be well-prepared for hardware emulation. Module design and verification studied MathWorks workflow step by step. Matlab reference code was designed and optimized on algorithm level. Simulink model which contains the fixed-point implementation was simulated to be compared with Matlab algorithm for periodic discrete-time environment before synthesizing into VHDL. The Register Transfer Level Design was verified in cosimulation with Simulink model. Besides, UVM based verification was applied to use System Verilog as verification language to evaluate the fulfillment of functional requirements and guarantee design accuracy with bit-cycle level.

The Thesis presents the design module, which serves the purpose of noise cancellation based on adaptive LMS algorithm. The theory and mathematical model of the design module are explained. RTL reusability was achieved with the use of modular coding style to create instantiated functions. The implementation work was done adhering to Mathworks digital design flow. Additionally, no errors or bugs were found from the design module under verifications. The module passed all required functionality tests. Hardware deployment and the related challenges, such as IP core generation to be integrated with a register abstraction layer, could be innovated for future development of this Thesis project, since the design module was already modified to be modular and reusable to form a scalable architecture with generic parameter specifications.

| Keywords | Adaptive filter, UVM, finite impulse response, | digital design, | RTL |

|----------|------------------------------------------------|-----------------|-----|

|          |                                                |                 |     |

# Contents

| Lis | ist of Abbreviations |                                                              |    |

|-----|----------------------|--------------------------------------------------------------|----|

| 1   | Intro                | oduction                                                     | 1  |

| 2   | Theo                 | ory                                                          | 3  |

|     | 2.1                  | Adaptive FIR Filtering                                       | 3  |

|     | 2.2                  | Least Mean Squares Algorithm                                 | 4  |

|     | 2.3                  | Adaptive Noise Canceller System                              | 8  |

| 3   | Digit                | tal Design Flow, Languages and Tools                         | 9  |

|     | 3.1                  | Digital Design Flow                                          | 9  |

|     | 3.2                  | Hardware Design and Verification Languages                   | 11 |

|     |                      | 3.2.1 VHDL for RTL Design                                    | 11 |

|     |                      | 3.2.2 System Verilog for Verification                        | 11 |

|     | 3.3                  | Verification Flow and Universal Verification Methodology     | 12 |

| 4   | Desi                 | ign Specifications and Algorithm to Architecture             | 17 |

|     | 4.1                  | LMS Algorithm for Digital Design and Implementation          | 17 |

|     | 4.2                  | Design Configurations and Constraints                        | 20 |

|     |                      | 4.2.1 Floating-point Matlab Implementation                   | 20 |

|     |                      | 4.2.2 Floating-point to Fixed-point Conversion               | 21 |

|     |                      | 4.2.3 Coding Style                                           | 22 |

|     |                      | 4.2.4 Verification Requirements                              | 23 |

| 5   | Ada                  | ptive FIR Filtering Noise Cancellation Module Implementation | 24 |

|     | 5.1                  | Matlab Analysis and Implementation                           | 24 |

|     |                      | 5.1.1 Floating-point Matlab Implementation                   | 24 |

|     |                      | 5.1.2 Fixed-point Matlab Mathematical Testbench              | 30 |

|     | 5.2                  | Simulink Reference Modelling                                 | 31 |

|     | 5.3                  | Register Transfer Level Design with VHDL                     | 38 |

| 6   | Ada                  | ptive FIR Filtering Noise Cancellation Module Verification   | 42 |

|     | 6.1                  | HDL Testbench Generation and Simulation with Questa Sim      | 42 |

|     | 6.2                  | Code Coverage                                                | 45 |

|     | 6.3                  | HDL Cosimulation Verification                                | 47 |

|     |                      |                                                              |    |

|    | 6.4    | Functional Verification with Universal Verification Methodology | 49 |

|----|--------|-----------------------------------------------------------------|----|

|    | 6.5    | System Verilog Assertions                                       | 55 |

| 7  | Cond   | clusion                                                         | 60 |

| Re | ferenc | ces                                                             | 62 |

# List of Abbreviations

| ASIC | Application Specific Integrated Circuit           |

|------|---------------------------------------------------|

| AXI  | Advanced eXtensible Interface                     |

| DPI  | Direct Programming Interface                      |

| DSP  | Digital Signal Processing                         |

| DUT  | Design Under Test                                 |

| DUV  | Design Under Verification                         |

| EDA  | Electronic Design Automation                      |

| FEC  | Focused Expression Coverage                       |

| FIR  | Finite Impulse Response                           |

| FPGA | Field Programmable Gate Array                     |

| HDL  | Hardware Description Language                     |

| IEEE | Institute of Electrical and Electronics Engineers |

| IIR  | Infinite Impulse Response                         |

| IP   | Intellectual Property                             |

| LMS  | Least Mean Squares                                |

| RLS  | Recursive Least Squares                           |

| RTL  | Register Transfer Level                           |

| SoC  | System On Chip                                    |

|      |                                                   |

# SV System Verilog

- VHDL Very High Speed Integrated Circuit Hardware Design Language

- UVM Universal Verification Methodology

# 1 Introduction

For the decades, the tremendous development in digital signal processing area which is in relation to growing technologies allows digital design and hardware implementation of signal processing to practically implement mathematical computations and complex algorithms. If the signal statistics are available to define data properties, fixed algorithms could be appropriately selected to be processed easily. Despite that, to track the statistical variations of signal over time in a nonstationary environment, its algorithms to be determined in advance are no longer efficient. The solution for this challenge is to use adaptive filter that automatically adapts to input characteristics change and noise cancellation by iterative estimation of configured parameters. Therefore, from this motivation, the Thesis work was to implemented to present the overall process of how to set up the adaptive noise cancellation module step-by-step from fixed-point conversion, reference modeling, RTL design with HDL testbench integration and UVM-based verification.

The goal of the Thesis work was to design, implement and verify an adaptive FIR filtering noise cancellation module coded in hardware description language according to the predefined design specifications and reference algorithms written by Matlab. The design had to be configurable with modular coding style that it can be reused in future university studies or innovation projects. Moreover, the design module is bit-exactly verified in UVM test bench against the implemented fixed-point Simulink reference model with provided configured parameters to confirm that the module is functioning bit-to-bit accurately as specified.

The HDL of choice for the project was Very High Speed Hardware Description Language version 1993, Institute of Electrical and Electronics Engineers standard 1076-1993. VHDL was chosen for its proven reliability and manufacturability in designing Application Specific Integrated Circuits and compatibility with virtually every commercially available design and verification tool [19;11,9].

The verification language used in the project was System Verilog, IEEE standard 1800-2005 [20]. SV is a higher-level, more versatile and less verbose language to design complex test environments with. SV and VHDL can also interface with each other to an sufficient degree and passing signals from design language to another is reasonably simple to do. SV is also a widespread, standardized, well supported and documented HDL.

[11,9] The universal design methodology based test environment was written almost completely in SV [21].

The mathematical algorithm is constructed to describe adaptive FIR filtering process for noise cancellation. Matlab numerical computation based on the configured use case is to generate compatible input sources then run its theoretical test to capture output data for simulation graphical plots of the compared results. For floating-point to fixed-point conversion, Simulink reference model is generated according to the verified Matlab algorithm to be against the register transfer level description of the module during configured sample time simulation run. This model was used for generating reference data under DPI-C code format for the UVM testbench which HDL entities were binding during parallel test simulation. The output data generated by RTL was compared to the data output from the Simulink fixed-point mathematical model simulation.

The UVM test bench utilized was to verify DUT at bit level for test cycles and the electronic design automation tools used in verification management are capable of doing not only thorough code coverage analysis but also functional assertions.

# 2 Theory

The theoretical background for the Adaptive FIR Filtering Noise Cancellation module is presented in this chapter. The main theoretical concepts behind LMS design and brief descriptions of how to operate adaptive noise cancellation in details are introduced.

# 2.1 Adaptive FIR Filtering

Adaptive filters are digital filters which have a set of coefficients to be changed under step adaptations in order to reach to the optimal convergence [4,421]. Adaptive algorithm would attempt to track the statistical changes in the input signals, the optimum solution is dependent on its inherent convergence rate versus the speed of input data characteristics [1,23]. The optimization criterion to be considered is the average mean square of error difference between filter output and desired signal value. During filter coefficients adaptation, the mean square error converges step-by-step to its minimal value. This state is said to be the optimal state at which the filter output matches very closely to the desired signal. According to the optimized algorithm, the determined transfer function is controlled by variable parameters. It means the adaptive filters self-adjust with recursive algorithm to compute updated filter weights. [1,30-31.]

Normally, when the signals start from some predetermined set of initial conditions to know their priori information, it is simple to process with the fixed algorithm after a number set of iterations. But in a nonstationary environment, it no longer works as desired. [1,22-23.] Due to the special nature mentioned above, especially the tracking capability for time variation of input data, adaptive filter has been selected for practical use cases and has become an important part of DSP applications like channel equalization, echo cancellation or adaptive beamforming. The basic function comes down to the adaptive filter performing a range of different tasks, namely, system identification, inverse system identification, noise cancellation and prediction. [1,37-38.]

Although both IIR and FIR filters have been considered for adaptive filtering, the FIR filter is by far the most practical and widely used. The FIR filter has only adjustable zeros to guarantee filter stability without the need of poles adjustments as in adaptive IIR filters. That is, adaptive FIR filters are always stable. [7,595.]

#### 2.2 Least Mean Squares Algorithm

The LMS algorithm is a stochastic gradient algorithm that it iterates each tap weight of an FIR filter in the direction of the gradient of the squared magnitude of an error signal with respect to the tap weight [1,40].

The LMS Algorithm is based on the FIR filter weights calculation. This algorithm is defined by these equations.

$$y(n) = w(n-1)u(n),$$

(1)

$$e(n) = d(n) - y(n),$$

(2)

$$w(n) = w(n-1) + \mu e(n)u(n)$$

(3)

Variable parameters are explained in table 1.

| Variable | Description            |

|----------|------------------------|

| n        | The current time index |

| Table 1. | Descriptions of variables from | adaptive LMS algorithm |

|----------|--------------------------------|------------------------|

|          |                                |                        |

| u(n) | The vector of buffered input samples at step n  |  |

|------|-------------------------------------------------|--|

| w(n) | The vector of filter weight estimates at step n |  |

| y(n) | The filtered output at step n                   |  |

| e(n) | The estimation error at step n                  |  |

| d(n) | The desired response at step n                  |  |

| μ    | The adaptation step size                        |  |

The implementation of the LMS algorithm [4,436-437] is concluded by the following steps:

- Initialize w0, w1, ... w(N-1) to arbitrary values where N is the FIR filter length.

- Read d(n), x(n), and perform digital filtering: y(n)=w0.x(n)+···+w(N-1).x(n-N+1).

- Compute the output estimation error: e(n)=d(n)y(n).

Update each filter coefficient using the LMS algorithm for k=0, …, N-1:

w(k)=w(k)+2µe(n)x(n-k).

The parameter  $\mu$  is the learning factor or step size that evaluates algorithm stability and its rate of convergence. It determines how fast the optimal weights are reached during step convergence. Necessary and adequate conditions of this parameter for the stability are discussed in detail in chapter 4 section 2.

For an efficient design and implementation of adaptive FIR filtering noise cancellation module under Thesis work objective, Least Mean Squares is the chosen algorithm for following reasons with its beneficial characteristics:

• It is a practical method to calculate a close estimation to optimal filter weights in real time. Accuracy is dependent on statistical sample size, since the filter weight values are based on the constant adaptive measurements of the input signals. [6,544.]

• Furthermore, its important characteristic of LMS algorithm is numerical robustness. To summarize, under the limited hardware resources, it is required to apply finite-precision arithmetic in linear adaptive filtering, the LMS algorithm generally is the preferred choice over another algorithm, for instance RLS algorithm [1,515].

Its computational complexity is simplified by a linear law that offers the ability to deliver a satisfactory in the face of unknown disturbance that can arise in practice. To be more specific, for an N-tap filter, the number of operations has been reduced to 2\*N multiplications and N additions per each coefficient update. Therefore, it has a relatively simple structure in comparison to RLS algorithm and the hardware usage is directly proportional

to the number of weights. This is suitable for real-time applications and is the reason for the popularity of the LMS algorithm. [13,21.]

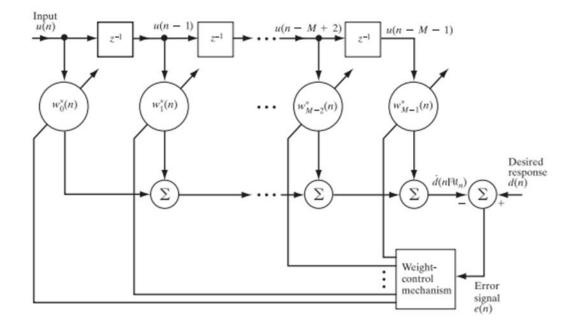

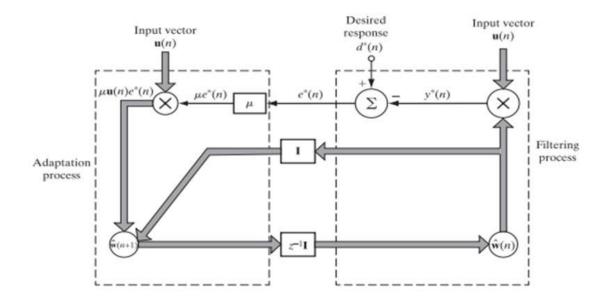

The LMS adaptive FIR filter architecture is as shown in figure 1 below. For every cycle, the adaptive filter automatically evaluates estimation error value for a new set of coefficients generation and computes the filter output based on applying these updates on the input data filtering.

Figure 1. Structure of an adaptive LMS FIR filter

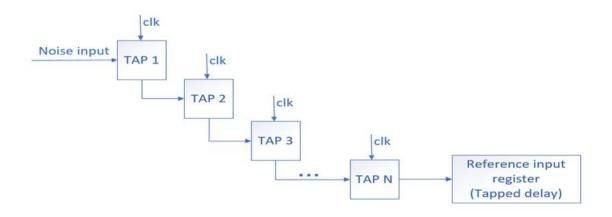

FIR filter, also referred to as a tapped-delay line filter or transversal filter, consists of three basic operations which are storage, multiplication, and addition [1,117]. These operations are described below:

The storage is represented by a cascade of M - 1 one-sample delays, with the block for each such unit labeled z-1. The number of delay elements used in the filter determines the finite duration of its impulse response. The number of delay elements, shown as M in the figure 1, is commonly referred to as the filter order. The delay elements are each identified by the unit-delay operator z-1. In particular, the delay process generates the tap inputs which represent the past values of the input. [1,117.]

The role of multiplication is that each multiplier in the filter is to multiply each compatible tap input by a filter coefficient. It forms respectively the scalar inner products of tap inputs and tap weights by using a corresponding set of multipliers. [1,117.]

At the final step, the adders in the filter is to sum the individual multiplier outputs to produce an overall response of the filter [1,117].

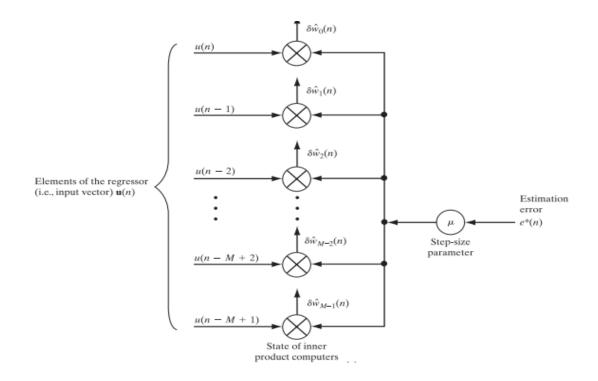

Figure 2. Detailed structure of the weight-control mechanism (Reprinted from [1,251])

For a specific analysis of adaptive weight-control mechanism, its function is to control the incremental adjustments applied to the individual tap weights of the FIR filter by exploiting information contained in the estimation error e(n). Figure 2 above presents the details of the adaptive weight-control mechanism. Specifically, a scalar version of the inner product of the estimation error e(n) and the tap input u(n - k) is computed for k = 0, 1, 2, . . . , M - 2, M - 1. The result obtained defines the correction w(n) k(n) applied to the tap weight w(n) k(n) at adaptation cycle n + 1. The scaling factor used in this computation is denoted by a positive number called the step-size parameter, which is real-valued along with the recursive computation of each tap weight in the LMS algorithm. [1,249.]

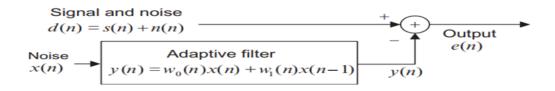

#### 2.3 Adaptive Noise Canceller System

Noise cancellation technology is a growing field that aims to cancel or at least minimize unwanted signal. In an adaptive noise canceller to be shown in figure 3 below, two input signals are applied simultaneously to the adaptive filter. The desired signal d is the contaminated signal including the clean original signal s and the noise where they are uncorrelated with each other. The signal x, is the generated noise by measuring corrupted signal, specified to be correlated with n. This signal x is the reference input to the canceller. The signal x is processed by the digital filter according to the adaptive algorithm to self-define filter coefficients to produce an estimate y. An estimate error of the clean original signal d. As a result, it produces the system output e expected to be the best estimate of the clean original signal s. Normally in practice, in the adaptive noise cancellation system, the clean original signal s, is the audio speech signal and the reference noise, is the signal generated from the Gaussian noise generator. [27;4,440.]

Figure 3. Noise Adaptive Canceller System Algorithm (Reprinted from [4,440])

DSP applications from adaptive noise canceller were summarized by Roger Woods [8]:

There are many applications in adaptive noise cancellation. It can be applied to echo cancellation for both echoes caused by hybrids in the telephone networks, but also for acoustic echo cancellation in hands-free telephony. Within medical applications, noise cancellation can be used to remove contaminating signals from electrocardiograms. Adaptive beamforming is another key application and can be used for noise cancellation. The function of a typical adaptive beamformer is to suppress signals from every direction other than the desired 'look direction' by introducing deep nulls in the beam pattern in the direction of the interference. A beamformer is a spatial filter that consists of an array of antenna elements with adjustable weights. The twin purposes of an adaptive beamformer are to adaptively control the weights so as to cancel interfering signals impinging on the array from unknown directions and, at the same time, provide protection to a target signal of interest. [8,30.]

metropolia.fi/en

# 3 Digital Design Flow, Languages and Tools

This chapter introduces the implementation and verification flows, EDA tools, languages and methods used to design, implement and verify the Adaptive FIR Filtering Noise Cancellation module. Digital design and implementation is presented first before logically moving forward onto the verification stage. Firstly, the digital design flow is introduced and the brief overview for each fundamental step is discussed. In addition, the hardware description language chosen for this project design and verification is mentioned. Lastly, the EDA tools required to be used in this project are demonstrated with functional features. In the verification sections, the verification flow is presented to show its important connections with the digital design flow. With the same description as in digital design sections, verification method and language utilized in this project are also mentioned with relevant features to be compatible with EDA tools.

#### 3.1 Digital Design Flow

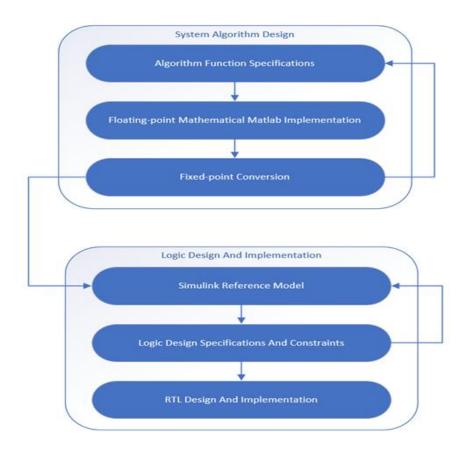

The design module is implemented according to Mathworks workflow [26]. The mathematical algorithm and functional specifications are prepared with a set of design constraints at the initial design phase. The functional specification outlined the range of capabilities and features the module should follow. The mathematical algorithm is experimented in detail under floating point implementation then it is converted to fixed-point model as a reference modular and configurable code which will be developed to create a Simulink golden model. Furthermore, there are Register Transfer Level implementations of corresponding Simulink components. A typical top-down digital design flow shown below in figure 4. The flow also comprises some feedback paths if needed for design iterations to be effectively adjusted at design stages. It aims to create module compatibilities between design algorithm and RTL implementation. One of the iterative feedback loops was in between fixed-point conversion step and algorithm functional specifications or between logic design constraints and Simulink reference model implementation. Fixed-point mathematical algorithm is the reference algorithm which would be verified to be in comparison with its floating-point implementation under the allowed predefined tolerance limitation. If there is a bad efficiency, based on available limited resources, for instance the maximum signal word length, the algorithm functional specifications at the early design phase must be reconfigured. Besides, RTL implementation

usually need a few design iterations before the Simulink model can be successfully realized in RTL because some Simulink constructs are not even feasible to implement synthesizable RTL design, leading to necessary adjustments.

Digital design flow consists of system analysis, design and verification of a system reference model, coding and verifying RTL description of the reference model.

System analysis is an early design phase, which includes system functional specifications, architecture specifications, coding the mathematical algorithms of the system. Architecture and algorithm choices during the system analysis affect system development and may have a great effect on design complexity [12,9].

The Simulink reference model to be developed from the mathematical algorithm describes the behavior of a system. RTL, which is hand-written based on the reference Simulink model, use HDL simulator to run the input data through HDL entities that these

data will be in comparison with output data generated by Simulink simulation for each bit cycle. RTL design codes are used to demonstrate hardware functionality.

# 3.2 Hardware Design and Verification Languages

# 3.2.1 VHDL for RTL Design

Very High Speed Integrated Circuit Hardware Design Language was originally developed by the order of the U.S Department of Defense (DoD) in the early 1980s. The purpose of VHDL was to document the behavior of the ASICs that were supplied to the DoD included in the equipment from their subcontractors. The next logical step was to develop a simulator capable of reading the created VHDL documents. Since the VHDL documents contained the exact behavioral model of the ASIC, logic synthesis tools were developed so that the HDL code could be turned into the definition of the physical implementation of the circuit. [11,36.] The Adaptive FIR Filtering Noise Cancellation module designed was written completely in VHDL.

# 3.2.2 System Verilog for Verification

System Verilog is a hardware design and verification language that is an extension to Verilog HDL. The first IEEE standard, 1800-2005, of System Verilog was based on Superlog design language and Open Vera verification language which were donated to the System Verilog project by Accellera and Synopsys respectively. In 2009 System Verilog was merged with base Verilog creating the SV IEEE 1800-2009 standard. The current standard of System Verilog is IEEE 1800-2012. [11,46-47.]

Test benches and verifying in general are not bound to the limitations of physical circuit design and because of this SV for verification has adopted many techniques from traditional programming languages such as C/C++, where SV adapted its syntax and Java [11,47]. SV for example supports object-oriented programming (OOP) techniques where objects are manipulated instead of data [20]. OOP is yet to make a breakthrough in HDLs but in test environments it is convenient to consider the different parts of the testbench as separate interconnected objects whose properties can be described and altered to suit the current verification task at hand. In SV objects are instances of classes which can inherit all or part of the properties of the class they are inherited from. OOP is a very useful programming paradigm for test bench since the code produced is very flexible, re-usable and transferable with little extra effort. [11,47.]

The verification environment used to verify the design module is written almost completely in System Verilog with DPI-C generated components and is based on UVM.

#### 3.3 Verification Flow and Universal Verification Methodology

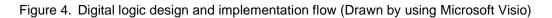

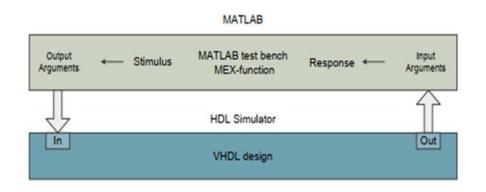

The verification flow applied for the Thesis project is shown in figure 5. At the initial design stage, design specifications are considered with a verification plan for feasibility. After this period, verifications are implemented to guarantee the module functional characteristics to be expected. That is, floating-point code and fixed-point mathematical code are used to verify the module functional characteristics. If any design error occurs during simulation, there would be an inevitable change on algorithm specifications. Simulink modeling is used to be as a reference algorithm due to its characteristics for visualization and sample-based simulation. That is, the design dataflow can be observed sample by sample during the simulation for fast error checking and easy debugging ability to intervene and adjust block properties to achieve model functional correctness. Configured diagnostics for the Simulink reference model are observed after simulation experiments to check model functionalities. In addition, Simulink components of each subsystem are utilized to be converted to DPI-C reference mathematic coding which is run under UVM test environment through Direct Programming Interface to generate the reference input stimuli and expected output data. These stimuli are driven into RTL DUT and RTL captured output will be in comparison with the available expected output from DPI-C coding parallel simulation. For RTL verification, HDL testbench is coded to verify RTL design in the specific use case to meet the functional specifications. Logic simulation is applied by utilizing this testbench. Later, to debug whether there is any design misoperation which differentiates RTL design from the reference model or not, HDL Cosimulation is used to set up mutual connections between Simulink and HDL Simulator. The identical stimuli are applied to both Simulink reference model and RTL DUT for parallel simulation then their outputs are captured to be compared with design goal which is to achieve the bitto-bit zero difference.

Figure 5. Digital verification flow and its relation to design flow (Drawn by using Microsoft Visio)

After passing these verifications, UVM is the higher-level verification method to be applied with System Verilog programming that engineers could have used for decades due to its configurable code features based on Verilog constructs.

Traditionally, the verification of HDL programs has been done in the same language the design was written. A testbench was designed for the design under test (DUT) and test stimulus was applied to the inputs of the DUT (HDL program) to check if the module functions correctly and the output is what was expected. This method of verification however is both time consuming and unreliable since every test case must be hand-crafted and exhaustively testing a big design is quite a task. Several verification methods were developed to tackle this issue and after a long period of vendor specific verification methods, the Universal Verification Methodology (UVM) was born. UVM is a standardized

methodology now supported by all the major simulator vendors. The UVM class library brings a lot of automation to the SystemVerilog language such as sequences, data automation features and macros. With UVM it is possible to create reusable, automated and adaptable test environments that accelerate the verification of complex hardware designs and make it possible to achieve much better test coverage with reduced effort compared to the traditional testbench-design approach. [20;21;11,46.]

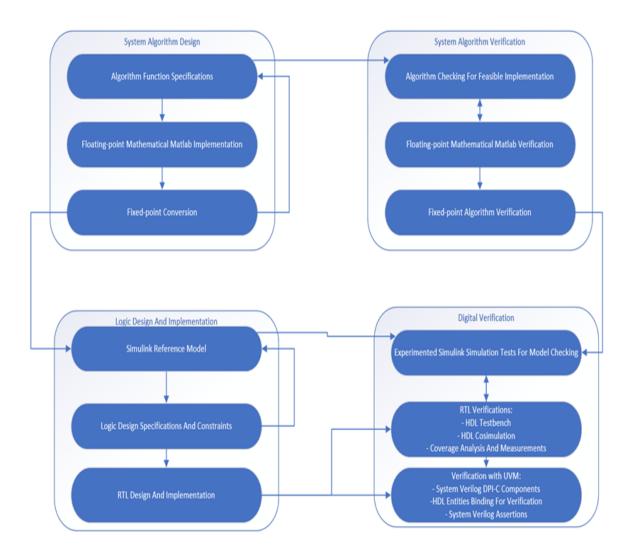

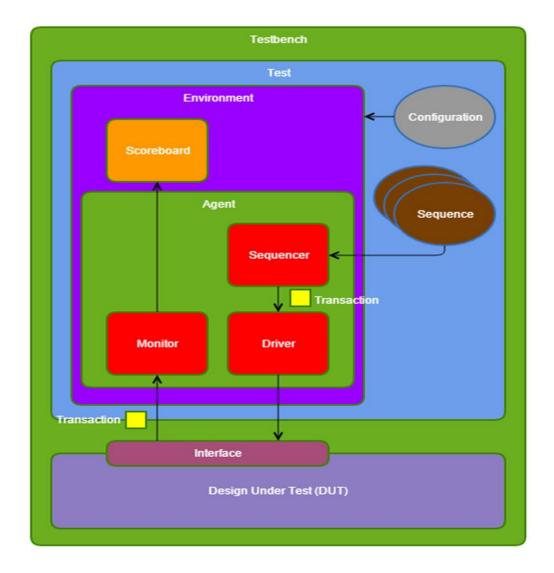

Figure 6. Verification Component Environment with UVM library classes (Reprinted from [11,53])

Verification components such as sequencers, monitors, drivers and agents are built using the blocks found from the UVM class library. The UVM classes from the UVM Class Library provide the building blocks needed to quickly develop well-constructed and reusable verification components and test environments in System Verilog as presented above in figure 6. The classes contain verification specific features for easier building of verification components. The UVM Class Library also provides utilities for debugging with user-controlled messages that can be used, for example, to report failures and the status

of every test operation on any level of the testbench, even globally. To be more precise, the UVM classes and utilities are divided into categories pertaining to the specific roles or functions such as UVM core base class, reporting classes provide a facility for issuing reports with consistent formatting and configurable side effects based on design verbosity and severity, factory overrides to manufacture UVM objects and components, phasing capability, configuration database, type parameterized data structures, and UVM reusable and configurable verification components. [21;11,53.]

Below are the main UVM verification components [11,53-54] explained briefly:

• Data item: Any input to the DUT network packets, buses, transactions or protocol values and attributes.

• Driver: Emulates the logic driving the DUT. Accepts data input which it can sample and feed to DUT.

• Sequencer: Stimulus generator that feeds the driver.

• Monitor: A passive entity that samples DUT signals. Monitors collect coverage information and perform the checking of the data.

• Agent: An agent encapsulates drivers, monitors and sequencers to simplify the usage of verification components by providing an abstract container which can perform a complex task without independently configuring every component.

• Environment: Top-level component of verification components and agents has the configuration properties for customization and re-use of the whole component topology without altering the internal components.

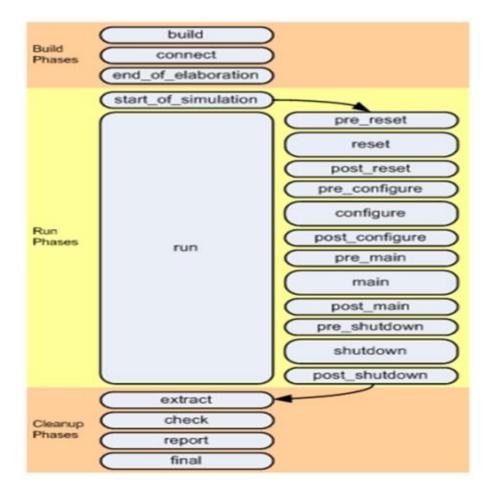

Figure 7. The UVM Phases (Reprinted from [17,11])

The UVM uses phases which are described in detail in figure 7. It allows a consistent testbench execution flow during simulation. There are three different groups of phases executed in the following order [17,11.]:

- Build phases: where the testbench is configured and constructed.

- Run-Time phases: where time is consumed in running the testcase.

- Clean-up phases: where the results of the testcase are collected and reported.

# 4 Design Specifications and Algorithm to Architecture

The Adaptive FIR Filtering Noise Cancellation module updates the filter weights based on LMS algorithm as FIR filtering procedure. The original input signal source is a complex-valued sinusoidal signal which is stimulated with configured length. The noise source is randomly generated then being filtered by FIR filtering process to create the corrupted noise. After the addition of the original input and the corrupted noise, the result of this procedure is the desired signal source which will be scaled for fixed-point implementation.

Before adaptive FIR filtering implementation, through configured tests, adaptation step size is selected to optimize the adaptive filtering process.

The tapped delay noise input and the estimation error output after each adaptive filtering procedure are used to calculate the updated filter weights based on adaptation step size.

4.1 LMS Algorithm for Digital Design and Implementation

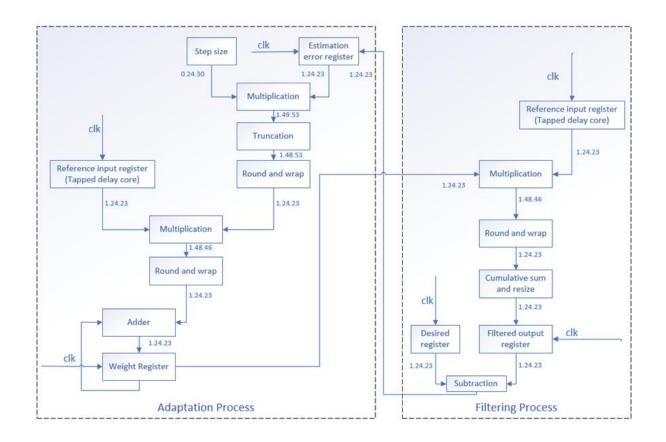

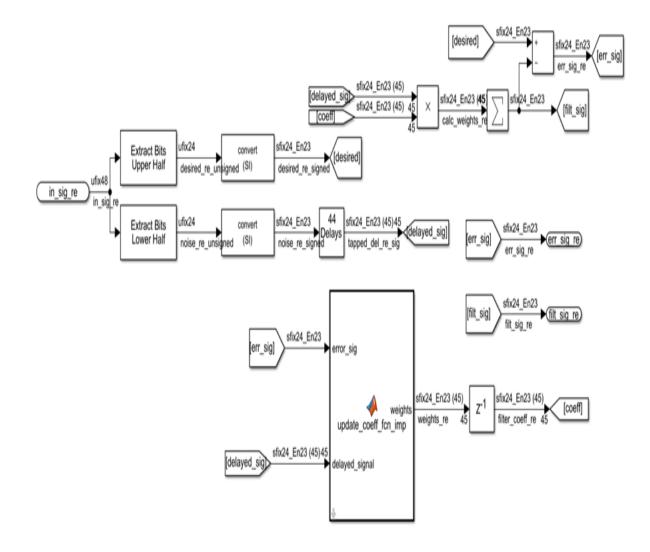

Based on the diagram as in figure 8, LMS algorithm consists of two basic processes that continually build mutually:

• Filtering process: filter output computation includes FIR filter design of noise input based on updated weights to get the calculated filtered signal and the subtraction of this filtered signal from the desired input signal to obtain the estimation error output.

• Adaptation process consists of weight update logic, tapped delay input processing, weight update controller.

Figure 8. Signal-flow graph representation of the LMS algorithm (Reprinted from [1,267])

The specified architecture is required to perform a design bit-level architecture for vectorvector multiplication used for output calculation with finite convolution sum applied algorithm.

Figure 9. Detailed RTL architecture of LMS algorithm (Drawn by using Microsoft Visio)

A detailed top-level module architecture is demonstrated in figure 9. It contains two partial designs: filter weights adaptation and filter output computation. The left-side design describes how the filter coefficients adapt to the optimal solution. For each valid clock cycle, the delayed input is generated from Tapped Delay core. The estimation error register will multiply by the fixed step size parameter, then the result will go through truncation, round and wrap procedures respectively. This result called adaptive correction will continue to multiply by the delayed input before rounding and wrapping to get the needed offset for weights adaptation. The addition between the weight offset and the weight register is to update to create a new set of filter coefficients. Meanwhile, filtering process is parallelly operated, which can be seen in detail at the right side of the figure 9. It describes the filter output computation. To be more specific, for each valid clock cycle, there occurs the multiplication between the generated set of filter weights and the delayed input to result in the output array with its size as the filter length order. After round and wrap, cumulative sum of elements and resize procedures, the final filtered output is used for subtraction operation based on noise cancellation algorithm to obtain the estimation error register. The Q-format [10,530] to be shown for each signal are configured in advance, is 1.24.23 that it means the signal is represented in signed binary format, 24 is the word length and 23 is the fractional length. In summary, these two design processes operate simultaneously and have a mutual impact on each other.

Figure 10. Tap delay processing of RTL Tapped Delay core (Drawn by using Microsoft Visio)

The Tapped Delay core for the adaptive noise cancellation module is shown in figure 10. In the tap processing, each tap is controlled by the valid clock signal. The input from each tap is shifted and stored to be combined with the next tap input after one-cycle delay operation. The reference noise input is propagated through all taps and automatically replaced by shift arithmetic process. [27.]

Figure 11. Weight update control mechanism for RTL (Drawn by using Microsoft Visio)

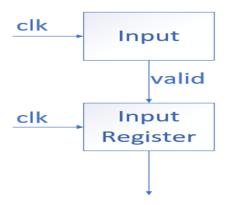

Weight update control mechanism is shown in figure 11. For every rising edge of the clock signal, the weight update process evaluates the valid signal which enables the register operation for signals to be used for mathematical computations.

4.2 Design Configurations and Constraints

The LMS algorithm designed for adaptive FIR filtering noise cancellation module is complex in the sense that the input and output data as well as the tap weights are all complex valued.

To be more specific, Matlab implementation, floating-point to fixed-point conversion, coding style and verification functional requirements are the considered aspects at the early design period to specify detailed variable parameters for design compatibility as well as its configurability.

#### 4.2.1 Floating-point Matlab Implementation

Relevant parameters related to adaptive LMS FIR filtering algorithm is configured as below:

• FIR filter length is 45, which is not only sufficient for coefficient adaptation but also an effective tap order number for FIR filtering.

• Stimulus length is 1000, which is high enough to allow an effective design functional characteristics observation.

• Scale Factor Adjustment: It is acceptable for accuracy limitation when transitioning from a floating point to a fixed-point representation. The conversion method is to keep a limited number of decimal digits. Normally, two to three decimal places method is appropriate for digital filter processing. Therefore, the scale factor can easily be obtained by multiplying the data values by 100 and divide the calculated values by 100 to recover the anticipated value. [13,24-25.] For complex signal, the common scale factor is the maximum value between the calculated scale factor of real part and the another one of imaginary part to guarantee that the output values are in the interval [-1, 1].

• Clean original input signals is a complex-valued sinusoidal signal which includes in dependent sinewave sequences containing the sine of elements over the domain which ranges are proportional to  $(-\pi,\pi)$  with multiplying constants of 5 and 6 respectively. Their step-incremental values are also in the interval [-1, 1] with a determined range which is corresponding to the configured stimulus length. Therefore, signal resolution is about 6.23\*10^-3 (radians).

• The noise input is generated as a random Gaussian noise sequence to be scaled by dividing by the common scale factor. The correlated noise input is generated by using a 22-th order window-based FIR bandpass filter with passband  $0.35\pi \le 0.65\pi$  rad/sample. The desired input is an addition of the clean sinewave input and the correlated noise input after being scaled by dividing by the common scale factor.

• The necessary condition for the step size parameter u to satisfy the convergence time constant is  $0 < u \ll 1$  [3,296]. In addition, if u is made too large then the algorithm becomes unstable. Therefore, u is determined to be optimal by test experiments using Matlab coding with pre-defined conditions.

# 4.2.2 Floating-point to Fixed-point Conversion

Floating point circuits have higher power consumption and lower performance compared to fixed point. For the vast majority of DSP applications, fixed point arithmetic is suitable, especially FIR filtering algorithm. [9,545-546.] For fixed-point conversion, signal dynamic range is mapped into the limited fixed-point precision [2,366].

Using finite word lengths prevents us from representing values with infinite precision, inaccurate arithmetic results. The level of output roundoff noise in fixed-point implementations can be reduced by increasing the word length. [5,647.]

The value bit width of 24 is chosen to be configured for quantization process due to its step resolution of 1/8388608 which works out to 1.192 \* 10-7, leads to the significant reduction of error percent of signal level. To perform mathematic computations in RTL design, Q1.23 format to represent signed values with fraction bits of 23 is used.

The next finite word-length effect to be considered is data overflow. Round and wrap on overflow are the chosen method due to hardware resource accuracy minimization, especially suitable for configured bit-level design. For addition and multiplication processes in RTL coding, the results are always truncated to Q1.23 format to meet the data bit width requirements as configured before.

# 4.2.3 Coding Style

MATLAB is generally used for algorithm design of a system for fast simulation and verification purposes of the behavioral model. To produce rational HDL code, the algorithm should be written from the hardware perspective. Algorithm models are often written into simulation optimized vector operations that create parallel structures and copies of combinational logic blocks in hardware. To create synthesizable MATLAB code, the structure must be correct. Register modeling is done through "persistent" variables. The variables that are wanted to save their states are defined in MATLAB function as persistent and these variables generate registers into RTL. [12,21-23.]

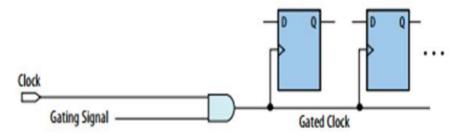

Gated clocks turn a clock signal on and off using an enable signal that controls gating circuitry. When a clock is turned off, the corresponding clock domain is shut down and becomes functionally inactive.

#### **Gated Clock**

#### Figure 12. Gated clock method to reduce power consumption (Reprinted from [22,12])

RTL implementation uses gated clock method as described in detail in figure 12 is utilized to reduce power consumption in device architectures by effectively shutting down portions of a digital circuit when not being in use [22,12].

# 4.2.4 Verification Requirements

All-passed verification from simulation-based verification with HDL testbench, bit-accurate parallel verifications with HDL Cosimulation and most importantly, UVM testbench that use constrained stimulus generation and functional coverage methodologies is the must-meet design goal. Apart from modular and reusable coding style, specifically for the mathematical algorithm, Matlab implemented coding is re-quired to be in separate functions which are targeted to a dynamic system.

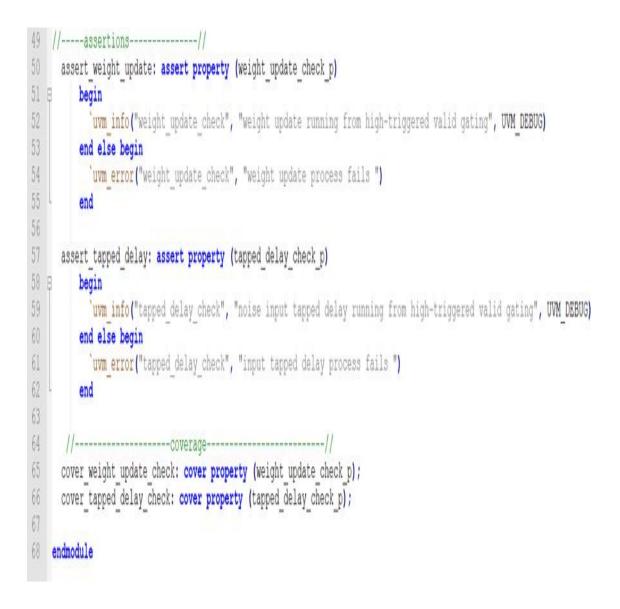

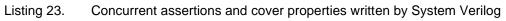

In addition, the structural coverage analysis with code coverage result of 100% along with all concurrent System Verilog assertions evaluated to be passed are the fundamental factors to clearly demonstrate design functional correctness.

# 5 Adaptive FIR Filtering Noise Cancellation Module Implementation

# 5.1 Matlab Analysis and Implementation

# 5.1.1 Floating-point Matlab Implementation

When the LMS algorithm is operating in a limited-precision environment, the point to note is that the step size parameter may be decreased only to a level at which the degrading impacts of round-off noises in the tap weights of the finite-precision LMS algorithm become significant [1,515].

In addition, as mentioned in section 4.2.1, step size that is too small increases the time for filter convergence or that is too large may cause the adaptive filter to diverge [27]. Therefore, to be in compliance with the step size condition, the step size u must be 0 < u << 1.

```

coeff_len = 45;

mu = 0.008% Set the step size for algorithm updating.

lms = dsp.LMSFilter(coeff_len,'Method','LMS',...

'StepSize',mu,'InitialConditions',0);

[~,e] = lms(noise,d);

L = 1000;

plot(0:999,signal(1:1000),0:999,e(1:1000));

title('Noise cancellation performance by the LMS algorithm');

legend('Actual original signal','Filtered error signal after noise reduction',...

'Location','NorthEast')

xlabel('Time index')

ylabel('Signal value')

```

Listing 1. Matlab implementation for adaptation step size test selection

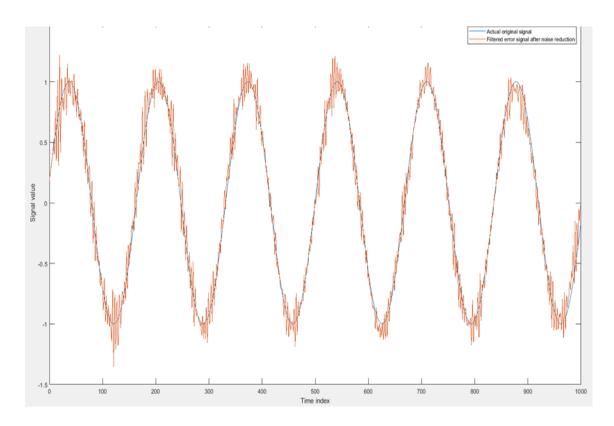

As seen in listing 1, the design configurations are fixed as specified in section 4.2.1 for input signals, the pre-defined filter length of 45 taps and the stimulus length of 1000. The available Matlab supported system object dsp.LMSFilter is utilized to compute estimation error output of the adaptive LMS filter according to the step size parameter which is experimentally determined. XY plot is used to show the output signals over time.

In figure 13, the blue signal is the clean original sinusoidal wave which runs at the same time with the filtered output signal which is the red one. The optimal solution is reached when the error difference between these two signals is at the minimum value. Therefore,

after test experiments with gradual reduction of step size parameter, 0.008 is the best choice because it is small enough but efficient to meet the design requirements to get the optimal convergence.

Figure 13. MATLAB GUI displaying the result of step size test selection after simulation

After defining the fixed adaptation step size, other design specifications must be configured independently as shown in listing 2. That means it is easy and convenient to modify if there is any change from the design algorithm. Matlab top-level design and Simulink reference model import this configuration as a design callback.

```

function config = init_config()

config.simtime = 10;

config.stim_len= 1000;

config.reset_weights =false;

config.update_weights = true;

config.coeff_len = 45;

config.del_num = 44;

config.step_size = 0.008;

end

```

Listing 2. Matlab function for initial design configurations

The detailed declaration for reference inputs of the Matlab mathematical testbench are shown in listing 3. These input declarations are to follow the design specification specified in section 4.2.1. The two inputs, which are the reference noise and the desired signal, are both generated in the sense of complex values. Moreover, window-based FIR filter design with the usage of dsp.FIRFilter system object is to generate correlated noise from original noise input. It uses a Hamming window to design a 22-th order FIR bandpass filter with passband  $0.35\pi \le \omega \le 0.65\pi$  rad/sample. The correlated input will be added to the clean sinewave to form the desired signal. Obviously, the scaling method is applied for original noise input and desired signal to adjust their value ranges to be in the interval [-1, 1].

```

% Create filter structure to generate correlated noise from noise input

filt2 = dsp.FIRFilter(...

'Numerator', fir1(22, [.35, .65]));

rng('default');

x = complex(randn(stim len,1),randn(stim len,1)); % Generate the noise input

% Scaling the noise input to +/- one

scale noise = max([abs(ceil(real(x)*100)/100); abs(ceil(imag(x)*100)/100)]);

x = x/scale noise;

% Generate the original input signal ( sinewave/random sequence)

w = [-0.99*pi:1.98*pi/(stim len-1):0.99*pi] ;

stimulus = complex(transpose(sin(6*w)),transpose(sin(5*w)));

d = step(filt2,x) + stimulus;

% Correlated Noise + Input Signal

% Scaling the desired signal to +/- one

scale signal = max([abs(ceil(real(d)*100)/100); abs(ceil(imag(d)*100)/100)]);

d = d/scale signal;

noise in = x ;

desired in = d ;

```

Listing 3. Input declarations for adaptive FIR filtering noise cancellation testbench

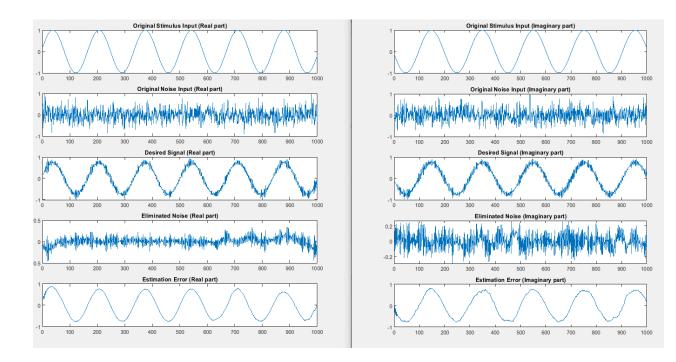

Down to the verification of the Matlab testbench as can be observed in listing 4, it calls the main implementation of adaptive LMS FIR filtering noise cancellation for separate data paths. Because both of two inputs are complex-valued format, to implement the adaptive LMS algorithm, their data paths are divided into real path and imaginary path. Each data path is independent to implement the adaptation process before complexvalued combination only at the final stage to get the final outputs. Therefore, there are two separate comparison plots for each data path.

```

figure('Name', [mfilename, '_signal_plot']);

subplot(5,1,1), plot(stim_re), title('Original Stimulus Input Signal (Real part)');

subplot(5,1,2), plot(x_re), title('Original Noise Input Signal (Real part)');

subplot(5,1,3), plot(d_re), title('Desired Signal (Real part)');

subplot(5,1,4), plot(y_re), title('Filtered Signal (Real part)');

subplot(5,1,5), plot(err_re), title('Error Signal (Real part)');

```

```

figure('Name', [mfilename, '_signal_plot']);

subplot(5,1,1), plot(stim_im), title('Original Stimulus Input Signal (Imaginary part)');

subplot(5,1,2), plot(x_im), title('Original Noise Input Signal (Imaginary part)');

subplot(5,1,3), plot(d_im), title('Desired Signal (Imaginary part)');

subplot(5,1,4), plot(y_im), title('Filtered Signal (Imaginary part)');

subplot(5,1,5), plot(err_im), title('Error Signal (Imaginary part)');

```

```

Listing 4. Call to the main design implementation from Matlab testbench and graphical plots of outputs after test simulation

```

The design goal is to implement design code to be configurable and reusable that there are modular functions coded for partial designs. Besides, to register the filter coefficients for Matlab mathematical algorithm, persistent variable declaration is used as can be seen in listing 5.

```

% register filter coefficients

persistent filter_coeff;

if isempty(filter_coeff)

filter_coeff = zeros(1,coeff_len);

end

```

Listing 5. Persistent variable usage for RTL description of filter weights

Adaptive LMS FIR filtering noise cancellation implementation is mainly divided into three modular functions to be shown in detail in listing 6, listing 7 and listing 8. These functions aim to be the design callbacks when the top-level design call them to perform FIR filtering and weight update process before output computation at the end of each step adaptation.

```

function tap delay = tapped delay re(input, coeff len)

% The Tapped Delay function delays its input by the specified number

% of sample periods, and outputs all the delayed versions in a vector

% form. The output includes current input

persistent u d;

if isempty(u d)

u d = zeros(1, coeff len);

end

a=zeros(1,coeff len);

for i=1: (coeff len-1)

if i == (coeff_len-l)

a(i) = u_d(i+1);

a(i+1) = input;

else

a(i) = u_d(i+1);

end

end

tap delay = a;

u d(:) = a ;

end

```

#### Listing 6. Tapped delay Matlab function

As seen in listing 6 above, the noise reference input is delayed at each simulation step to form 45 taps which is previously defined as exactly equal to the filter coefficient length. The persistent variable u\_d is responsible to store the tap input which is in vector form for shifting process when the top-level design calls the tapped delay function.

```

function weights = update_coeff_fcn_im(step_size, error_sig, delayed_signal, filter_coeff, reset_weights,update_weights,coeff_len)

% This function updates the adaptive filter weights based on LMS algorithm

step_sig = step_size .* error_sig;

adaptive_correction = delayed_signal .* step_sig;

updated_weight = adaptive_correction + filter_coeff;

if reset_weights

weights = zeros(1,coeff_len);

elseif update_weights

weights = updated_weight(1:coeff_len);

else

weights = filter_coeff;

end

```

Listing 7. Weight update logic Matlab function

The main adaptation procedure is described in listing 7. The weight update logic is implemented step-by-step in a clear coding style, follows the LMS reference algo-rithm. The Matlab code is to use reset\_weights variable and update\_weights variable to set the weight update control mechanism.

```

function output = cusum_re(input)

output = 0 ;

for i = 1:numel(input)

output(:) = output + input(i) ;

end

end

```

Listing 8. Cumulative sum of elements Matlab function

FIR Filtering process is simply described in listing 9. To be more specific, after vectorvector multiplication between tapped delay input and the filter coefficient set, cumulative sum of elements procedure shown in detail in listing 8 is implemented to calculate the filtered signal based on the computed filter weights as the input variable.

```

% Create filtered signal using FIR filter algorithm

weight = delayed_signal .* filter_coeff;

filtered_signal = cusum_re(weight);

```

Listing 9. Filtered output computation procedure from Matlab reference design

After design steps of Matlab mathematical algorithm mentioned previously, the Matlab testbench is run to verify adaptive FIR filtering noise cancellation reference design. The plot of outputs for each data path is shown in figure 14.

Figure 14. Graphical plot to show Matlab testbench outputs after simulation

The adaptive FIR filtering noise cancellation is successfully operated. The desired signal is the addition of the clean sinewave stimulus and the noise reference input. To be compared with the desired signal, the estimation error signal reached the cleaner version due to noise elimination. To be more precise, the estimation error is the result of the subtraction the FIR-filtering filtered output signal from the desired signal.

# 5.1.2 Fixed-point Matlab Mathematical Testbench

To implement floating-point to fixed-point conversion, fixed-point mathematics configuration is simply specified in Listing 10 below which is added to every Matlab floating-point code.

```

fim = fimath('RoundMode','round','OverflowMode','Wrap','ProductMode','FullPrecision','SumMode','FullPrecision');

dat = numerictype(1,24,23);

step_v = numerictype(0,24,30);

```

Listing 10. Matlab fixed-point mathematics configuration

As listing 10 demonstrated, step\_v is exceptional to be configure only for fixed-point step size while dat is configured for remaining signals.

## 5.2 Simulink Reference Modelling

Simulink is a graphical design tool that uses library blocks, MATLAB functions and System Objects to perform indicated tasks and functions. Simulink library contains huge selection of hardware optimized blocks. These blocks are divided into different categories to be integrated in SoC development. User-defined MATLAB function blocks and System Object blocks can be used to self-define design specific configurations or to reutilize available MATLAB mathematical computations. The blocks are built in Simulink modeling by referring the Matlab reference algorithm with fixed-point data types. A test bench in Simulink is built by driving all input variables into Device Under Test and capturing DUT outputs to be verified. The data is imported as streaming data with generic parameter configurations. [12,24-25.]

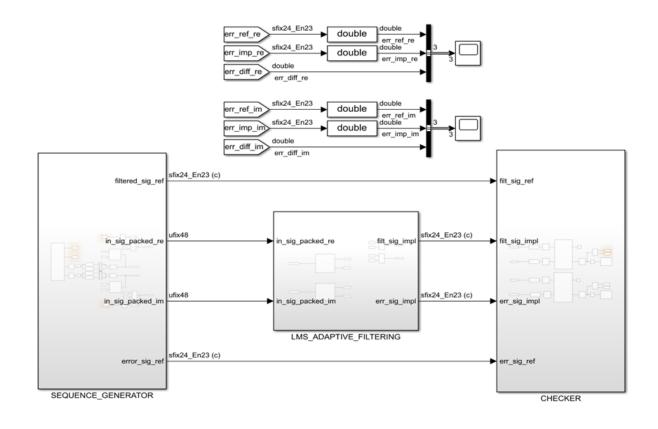

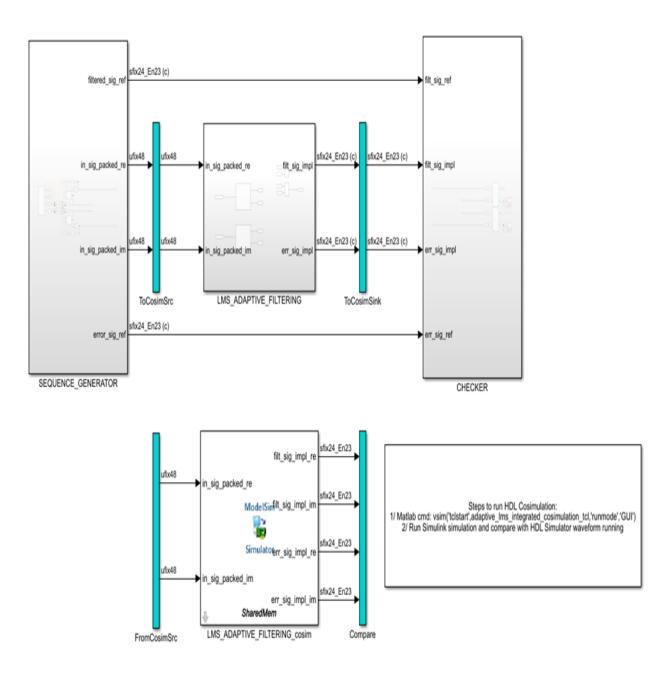

Simulink Reference Model implementation is based on Matlab fixed-point design algorithm. The top-level model is divided into three main parts shown in figure 15. The data flow goes left to right from sequence generation, main adaptive filtering design to model checker. Each module subsystem is designed in detail that can be seen in figure 16, figure 18, and figure 19.

### Figure 15. The top-level design of Simulink Reference Model

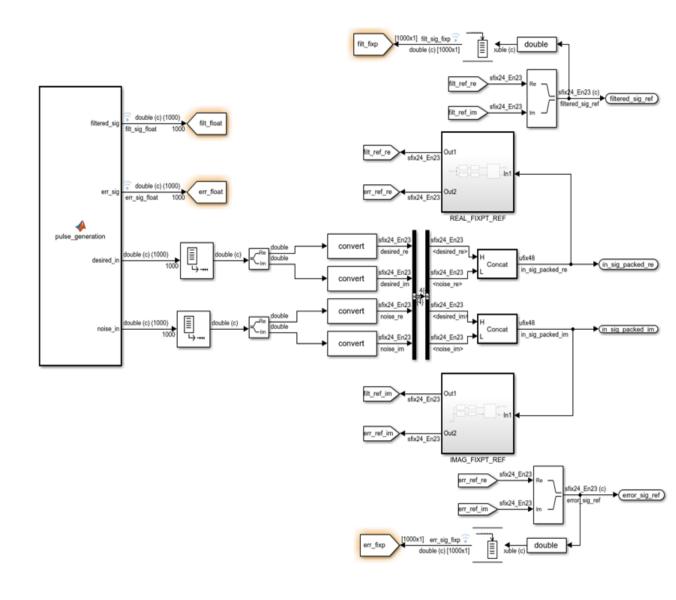

For a clear explanation, the sequence generator in figure 16 below is to generate the fixed-point inputs and the fixed-point expected outputs. The fixed-point inputs are driven into Simulink LMS Adaptive Filtering design to generate the corresponding implemented outputs which will be compared with the expected outputs. From the leftmost side, the pulse\_generation function imports the Matlab testbench as mentioned previously in Section 5.1.1 to generate the floating-point desired input and noise input which are data sets of 1000 complex-valued samples going through Simulink Unbuffer block to form scalar sequences during fixed-step simulation before splitting into real path and imaginary path. Then, for each path, their inputs will be converted to the fixed-point data with Q-format 1.23 data type.

Figure 16. Sequence generator to generate fixed-point inputs and fixed-point expected outputs based on Matlab reference algorithm

To create the expected outputs to be compared with Simulink simulated outputs, these fixed-point inputs implement the fixed-point Matlab testbench specified in section 5.1.2 as imported function shown in figure 17 below. Concurrently, for each data path, their fixed-point inputs are cross connected to have a new datapack in which the first half represents the desired input whereas the last half represents the noise input.

### Figure 17. Generation of expected outputs by importing the fixed-point Matlab testbench

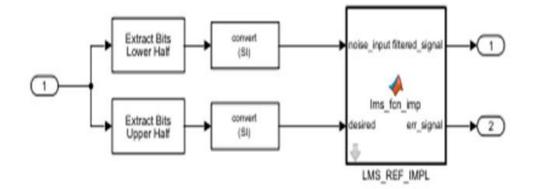

When it comes to the main adaptive LMS FIR filtering noise cancellation design, there are two 24-bits datasets extracted from the data packs derived from sequence generator. These indicated datasets, which are desired and noise reference, are the fixed-point inputs to implement the Matlab fixed-point algorithm. All of operations make the use of Simulink supported blocks to process left-to-right to abide by the dataflow as can be seen in figure 18. The only exception for not using Simulink block is the coefficient update procedure that uses the masked subsystem to call the Matlab fixed-point weight update logic function with specified design parameters, guarantees re-configurable data structure with modification of filter length variable. For more clear explanation, if the filter length parameter is changed to the large value for future innovation projects, the Simulink data model has to change significantly, especially creating more complicated cross connections in addition to large amounts of feedback paths for filter coefficient register, leads to the impossibility to create the functional model. Therefore, the available Matlab fixed-point weight update logic function is the optimal choice for weight update procedure.

Figure 18. Simulink LMS design to implement adaptive noise cancellation process

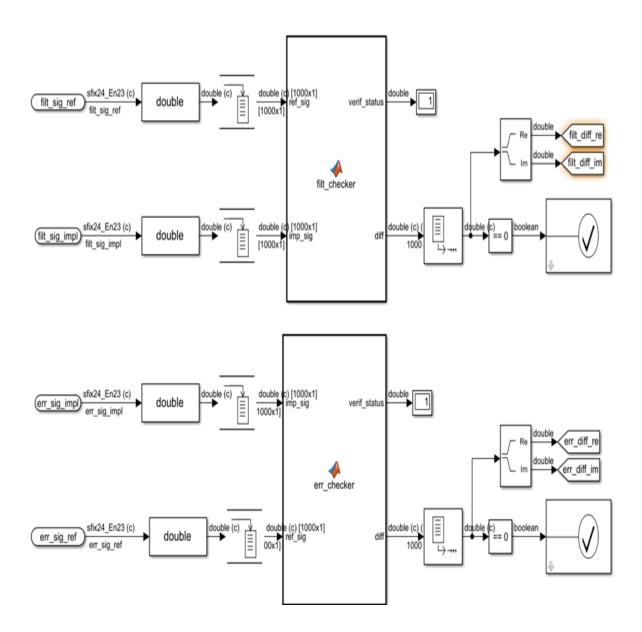

After adaptive noise cancellation implementation, to verify model functional correctness, the checker shown in figure 19 verifies the equivalence checking between the golden reference output derived from fixed-point Matlab testbench implementation and the another one achieved from Simulink simulation.

Figure 19. The checker to compare the implemented outputs with the expected outputs

This checker imports the Matlab Ims\_checker function demonstrated in listing 11 for the response checking of both filtered output and estimation error output. This function evaluates the size difference of the two inputs for dimensional comparability. The test result must be passed to move onto the next verification that compares the expected signal with the implemented signal for every corresponding element. The assertion messages will be displayed for compatible test cases during Simulink simulation.

```

function [verif status, diff] = lms checker(imp sig, ref sig )

ref dim = size(ref sig, 1);

imp_dim = size(imp_sig, 1);

if (ref_dim == imp_dim)

dim_assert = true;

else

dim assert = false;

end

diff = complex(zeros(ref_dim,1),zeros(ref_dim,1));

mis_var = zeros(ref_dim,1);

if dim assert

disp(' Dimension checking is passed.')

for i = 1:ref dim

exp = ref sig(i);

dut = imp sig(i);

diff(i) = abs(dut-exp);

% Values do not match

if ~isequal(dut,exp)

disp(' !!! Data does not match.')

verif status = 0;

% Something wrong. Find out which sample

fprintf(' mismatch at index %5f, expected_ref: %8f, dut_imp: %8f, diff: %9f, ratio: %5f \n', i, exp, dut, abs(dut-exp), dut/exp)

error('Data mismatch happens.')

else

% The reference signal matches the implemented signal (design

% under test)

disp(' Data matches.');

verif status = 1;

end

end

else

verif_status = 0;

error('Signal dimension checking is failed');

end

```

# Listing 11. Checker function to verify signal equivalence checking

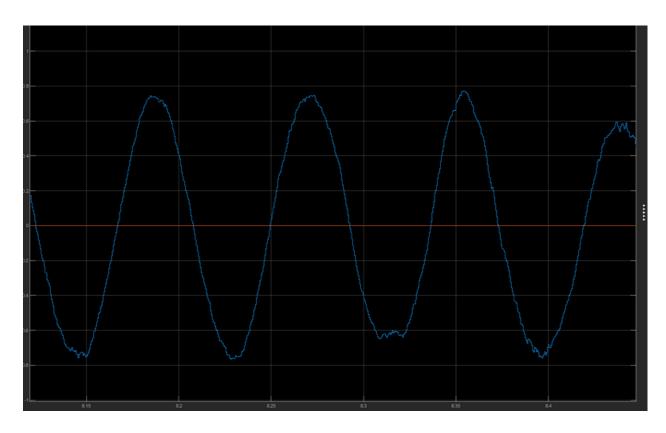

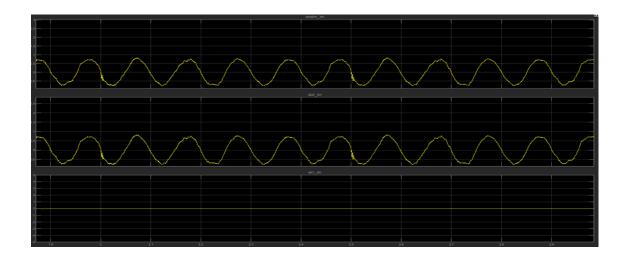

The final step to verify is to run the Simulink reference model. For detailed waveform analysis of the output signals which can be observed in figure 20, the blue signal is the sinusoidal wave of estimation error signal whereas the red line indicates the error difference of zero which is calculated by subtracting the Simulink implemented data from the Matlab reference data.

Figure 20. Graphical plot to show estimation error output and the zero difference between Matlab reference data and Simulink implemented data

In addition, the messages from Ims\_checker function for test-passed verification are on the Diagnostic Viewer display during Simulink simulation.

| 🍋 Diagnostic Viewer                                                                                                                                                                                     | _     |   | $\times$ |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---|----------|

| Diagnostics                                                                                                                                                                                             |       |   |          |

|                                                                                                                                                                                                         | earch | Ŷ | ÷        |

| adaptive_filter_Ims                                                                                                                                                                                     |       |   |          |

| Dimension checking is passed.<br>Data matches.<br>Data matches.<br>Data matches.<br>Data matches.<br>Data matches.<br>Data matches.<br>Data matches.<br>Data matches.<br>Data matches.<br>Data matches. |       |   |          |

Figure 21. Diagnostic viewer of checker function during Simulink simulation

As figure 21 illustrated, the messages mean the Simulink reference model is designed as exactly specified as Matlab reference mathematical algorithm.

### 5.3 Register Transfer Level Design with VHDL

The final design phase is to create Register Transfer Level descriptions of the Simulink attributes. The RTL designs are required to have integrated HDL coding style to validate the Simulink reference model.

All RTL implementations are coded in VHDL according to design specifications and constraints mentioned in chapter 4. To be more specific, fixed predefined design parameters are configured in LMS\_ADAPTIVE\_FILTERING\_pkg.vhd file as illustrated in listing 12. Apart from initial declarations of fixed parameters such as filter coefficient length and weight update control logics, the constant w\_data\_c of 24 is the common data word length configuration for all data signals which are design entity in-puts, entity outputs and the outputs of different binary arithmetic operations. Besides, w\_mult\_c of 48 and w\_adder\_c of 30 are the constants used for multiplication and finite convolution sum. Furthermore, data word length of step size is to obey the specified design specification that its fractional length is 30 and its word length is 24. In addition, it is fixed to be an unsigned binary of 0.008 which hexadecimal converted result is 83126F.

```

PACKAGE LMS_ADAPTIVE_FILTERING_pkg IS

constant w_data_c : natural := 1 + 0 + 23;

constant w_mult_c : natural := w_data_c * 2;

constant coeff_len : natural := 45;

constant msb_c : natural := coeff_len-1;

constant log_coeff_len : natural := 6;

constant w_adder_c : natural := w_data_c + log_coeff_len ;

constant reset_weights : std_logic := '0';

constant update_weights : std_logic := '0';

constant step_size_c : unsigned(w_data_c-1 DOWNTO 0) := to_unsigned(16#83126F#, w_data_c);

constant step_s_fracw : natural := 30;

```

TYPE vector of signed w data IS ARRAY (NATURAL RANGE <>) OF signed(w\_data\_c-1 DOWNTO 0); TYPE vector of signed w mult IS ARRAY (NATURAL RANGE <>) OF signed(w\_mult\_c-1 DOWNTO 0);

Listing 12. Data declarations of fixed parameters in HDL package file

As specified in section 4.2.2 about overflow handling and rounding, round and wrap on overflow is the chosen method to be coded as an HDL procedure that can be seen in listing 13. Its inputs are based on the following factors: rounding Most Significant Bit, rounding Least Significant Bit and wrapping Most Significant Bit. There are two concurrent procedures that the rounding procedure uses resize function to truncate input to

data with a new specified data width but retain the sign bit as can be seen in line 75 whereas the wrapping procedure is going through recursive OR operations with the usage of for loop as coded from line 80 to line 82 before using different bitwise calculations based on the wrapping theory to generate the wrap bit. The result from rounding and wrapping procedures is the addition of the rounded variable and the wrap bit. More-over, the cumulative sum of elements procedure is also directly coded at the top of the identical HDL package file as can be seen from line 45 to line 61.

```

44 PACKAGE BODY LMS_ADAPTIVE_FILTERING_pkg is

45 🛱 procedure cusum (

4.6

constant add len

: in natural;

constant expected_data_w : in natural;

47

signal in_sig : in vector_of_signed_w_data(0 to msb_c);

signal out_sig : out signed(w_data_c-1 DOWNTO 0)) is

48

49

variable inter_sig_v : signed(add_len-1 DOWNTO 0);

52 🛱 begin

inter_sig_v := to signed(16#000000#, add_len);

54

FOR i IN 0 TO msb_c LOOP

56

inter_sig_v := inter_sig_v + resize(in_sig(i),add_len);

END LOOP;

58

59

out_sig <= inter_sig_v(w_data_c-1 DOWNTO 0);</pre>

60

61

end procedure cusum:

62

63

procedure round_and_wrap (

64

constant rounding_msb

: in natural;

constant rounding_lsb : in natural;

constant wrapping_msb : in natural;

65

66

: in signed(w_mult_c-1 DOWNTO 0);

: out signed(w_data_c-1 DOWNTO 0)) is

67

signal in sig

68

signal out_sig

69

variable inter_a_v : std_logic;

variable inter_b_v : signed(1 downto 0);

variable inter_sig_v : signed(w_data_c-1 DOWNTO 0);

71

72

🖻 begin

74

--rounding procedure

inter_sig_v := resize(in_sig(rounding_msb downto rounding_lsb),w_data_c);

76

77

78

--wrapping procedure

inter_a_v := in_sig(0);

79

FOR i IN 1 TO rounding_1sb-2 LOOP

81

inter_a_v := inter_a_v OR in_sig(i);

END LOOP

83

84

inter b v := ('0' & (in sig(rounding lsb-1) AND (( NOT in sig(wrapping msb)) OR(inter_a v))));

85

86

out_sig <= inter_sig_v + inter_b_v;</pre>

end procedure round_and_wrap;

```

The main RTL coding for adaptive noise cancellation algorithm is separated into three partial operations which run simultaneously. RTL coding style uses rising clock edge to drive the signal logic and asynchronous reset which will be activated when the reset signal is asserted. To be more explicit, tapped delay processing described in listing 14 is to generate 45-taps noise reference input.

```

Tapped_Delay_process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

Tapped_Delay_reg <= (OTHERS => to_signed(16#000000#, w_data_c));

ELSIF clk'EVENT_AND_clk = '1' THEN

IF valid_in = '1' THEN

Tapped_Delay_reg(msb_c-1) <= noise_re_signed;

Tapped_Delay_reg(0 TO msb_c-2) <= Tapped_Delay_reg(1 TO msb_c-1);

END_IF;

END_IF;

END_PROCESS_Tapped_Delay_process;

tapped_del_re_sig(0 TO msb_c-1) <= Tapped_Delay_reg(0 TO msb_c-1);

tapped_del_re_sig(msb_c) <= noise_re_signed;</pre>

```

Listing 14. HDL procedure to create tapped delay signal from noise input

In addition, as can be seen in listing 15, adaptive weight update from line 90 to line 99 is to utilize mathematical computations based on adaptive LMS FIR filtering theory. For every clock cycle, valid signal starts filter coefficient registering.

```

90

step sig first <= step size signed * err sig re signed;</pre>

step sig cst <= step sig first(w mult c-1 DOWNTO 0);</pre>

91

92

round and wrap(step sig cst'length-1, step s fracw, step sig cst'length-1, step sig cst, step sig);

93

94

weights re gen: FOR i IN 0 TO msb c GENERATE

adapt corr cst(i) <= tapped del re sig(i) * step sig;</pre>

95

round and wrap(adapt_corr_cst(i)'length-2,w_data_c-1,adapt_corr_cst(i)'length-1,adapt_corr_cst(i),adaptive_correction(i));

96

updated_weight(i) <= adaptive_correction(i) + filter coeff re signed(i);

97

98

weights re(i) <= updated weight(i);</pre>

99

END GENERATE weights re gen;

Delay process : PROCESS (clk, reset)

BEGIN

103 E IF reset = '1' THEN

filter_coeff_re <= (OTHERS => to signed(16#000000#, w_data_c));

ELSIF clk'EVENT AND clk = '1' THEN

Ē

106 F

IF valid in = '1' THEN

filter coeff re <= weights re;

END IF;

109

END IF;

110

END PROCESS Delay process;

112

calc weights re gen: FOR k IN 0 TO msb c GENERATE

calc weights re cst(k) <= tapped del re sig(k) * filter coeff re signed(k);</pre>

114

round and wrap(calc weights re cst(k) 'length-2, w data c-1, calc weights re cst(k) 'length-1, calc weights re cst(k), calc weights re(k));

END GENERATE calc weights re gen;

116

117

cusum(w adder c,w data c,calc weights re,filt sig re signed);

```

Listing 15. RTL top-down adaptation process

As coded from line 112 to line 117 in listing 15, FIR filtering of the delayed noise input according to the updated filter coefficient set and the tap delay of noise reference is the vector-vector multiplication to create a new set of filter weights which then goes through the rounding and wrapping procedure. After that, the adaptive filtered output is generated by using cusum procedure declared in HDL package file for finite summation of the calculated filter weight.

# 6 Adaptive FIR Filtering Noise Cancellation Module Verification

The verification techniques used to verify RTL design of Adaptive FIR Filtering Noise Cancellation module are explained here and the results of these verifications are also presented. RTL design in this Thesis goes through multiple levels of verification. Queta-Sim as an HDL Simulator empirically checks simulation-based RTL functional character-istics with assertions and provides the design code coverage analysis. Besides, HDL Cosimulation establishes mutual connections between Simulink and QuestaSim for parallel simulations to guarantee that RTL design does what Simulink reference modeling expects under clock synchronization condition. Finally, an UVM based bit-exact simulation testbench is used to verify the specific use case. The HDL entities are integrated to the UVM environment. The DPI-C mathematical model, which is converted from the Simulink reference model, is to run to generate input stimulus and the reference output data. During UVM test simulation, the generated input stimulus will stimulate RTL entities then their output data will be captured to be compared with the DPI-C generated reference output data.

## 6.1 HDL Testbench Generation and Simulation with Questa Sim

This first verification to verify RTL design is to generate a HDL test bench to simulate HDL design files in QuestaSim simulator.

This test bench verifies the created HDL DUT against test vectors generated from Simulink reference model. The input stimulus and expected data, which are generated from Simulink simulation, are stored in data files (.dat). In detail, the input data are in\_sig\_packed\_re, in\_sig\_packed\_im and the output data are err\_sig\_impl\_re\_expected, err\_sig\_impl\_im\_expected, filt\_sig\_impl\_re\_expected, filt\_sig\_impl\_im\_expected that their data format is hexadecimal number. During HDL simulation, the HDL test bench will read the input stimulus derived from the input data files then drive these stimuli to DUT input ports as illustrated in listing 16. After that, the HDL testbench captures the actual DUT outputs which will be compared with the corresponding expected outputs stored in the output data files.

```

u_LMS_ADAPTIVE_FILTERING : LMS_ADAPTIVE_FILTERING

PORT MAP( clk => clk,

reset => reset,

valid_in => valid_in,

in_sig_packed_re => in_sig_packed_re_out, -- ufix48

in_sig_packed_im => in_sig_packed_im_out, -- ufix48

valid_out => valid_out,

filt_sig_impl_re => filt_sig_impl_re, -- sfix24_En23

filt_sig_impl_re => err_sig_impl_re, -- sfix24_En23

err_sig_impl_re => err_sig_impl_re, -- sfix24_En23

);

```

Listing 16. RTL entities binding to the HDL testbench

As can be seen in listing 17, for real data path, the process statement describes the procedure which opens in\_sig\_packed\_re.dat file to read the input stimulus as read\_data variable then stores it as a raw data for the registering process. Because stimulus capture is dependent on not only system clock signal but also intrinsic rdEnb variable value, there are two concurrent processes that the first one as coded from line 259 to line 266 is responsible to hold raw data at every rising clock edge to be driven into offset data if sequence reading is disabled, whereas the remaining one as coded from line 268 to line 275 is to immediately achieve raw data as an offset data if there occurs any change of raw data.

```

243

-- Data source for in_sig_packed_re

244

in sig packed re fileread: PROCESS (async time del, tb enb delay, rdEnb)

FILE fp: TEXT open READ_MODE is "in_sig_packed_re.dat";

245

246

VARIABLE 1: LINE;

247

VARIABLE read data: std logic vector(47 DOWNTO 0);

248

249

BEGIN

IF tb_enb_delay /= '1' THEN

ELSIF rdEnb = '1' AND NOT ENDFILE(fp) THEN

251 🖨

READLINE(fp, l);

HREAD(1, read_data);

254

END IF;

255

rawData_in_sig_packed_re <= unsigned(read_data(47 DOWNTO 0));</pre>

256

END PROCESS in sig packed re fileread;

257

258

holdData reg for sequence generator

259 🖨

stimuli_sequence_generator_process: PROCESS (clk, reset)

BEGIN

261

IF reset = '1' THEN

holdData_in_sig_packed_re <= (OTHERS => 'X');

þ

ELSIF clk'event AND clk = '1' THEN

264

holdData_in_sig_packed_re <= rawData_in_sig_packed_re;</pre>