# Motherboard design for an X-ray beam profile monitor system

Jussi Malin

Thesis

**Bachelor's degree**

-• ---

\_\_\_\_\_

## SAVONIA-AMMATTIKORKEAKOULU

| Koulutusala<br>Tekniikan ja liikenteen ala                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Koulutusohjelma                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                         |

| Elektroniikan koulutusohjelma                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                         |

| Työn tekijä(t)                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                         |

| Jussi Malin                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                         |

| Työn nimi                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                         |

| Röntgensäteilyn profiilinmittauslaitteiston emole                                                                                                                                                                                                          | vyn suunnittelu                                                                                                                                                                                                                                                                                                                                                                         |

| Päiväys 3.4.2012                                                                                                                                                                                                                                           | Sivumäärä/Liitteet 50/45                                                                                                                                                                                                                                                                                                                                                                |

| Ohjaaja(t)                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                         |

| Tohtori Gary Varner, University Hawaii at manoa                                                                                                                                                                                                            | , Yliopettaja Ari Suopelto, Savonia-AMK                                                                                                                                                                                                                                                                                                                                                 |

| Toimeksiantaja/Yhteistyökumppani(t)                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                         |

| University Hawaii, Instrumentation Development                                                                                                                                                                                                             | Laboratory                                                                                                                                                                                                                                                                                                                                                                              |

| Tiivistelmä                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                         |

| mittauslaitteistoon. Röntgensäteilyn mittalaitteisto<br>profiilin mittaukseen ja suuntaamiseen. Tavoit<br>mahdollistavat luotettavan ja suurinopeuksisen<br>nin. Suunnittelu tehtiin PADS-suunnitteluohjelmis                                              | emolevy 64-kanavaiseen röntgensäteilyn profiilin-<br>oa käytetään hiukkaskiihdyttimen elektronisuihkun<br>tteena oli suunnitella ja valmistaa piirilevyt, jotka<br>röntgensäteilyn profiilin mittauksen ja digitalisoin-<br>stolla Havaijin yliopiston mittalaitelaboratoriossa.                                                                                                        |

| tarkoituksena on nostaa hiukkaskiihdyttimen elel<br>ta korkeammaksi. Tämä voidaan saavuttaa joko<br>distamalla elektronisuihku pienemmälle pinta-a<br>mäksi valittiin elektronisuihkun pinta-alan piene<br>poikkipinta-ala vähenee mikrometrialueelta nano | päivitystä SuperKEKB-kiihdyttimeksi. Päivityksen<br>ktronisuihkun energia 20 kertaa alkuperäistä laitet-<br>nostamalla elektronisuihkun intensiteettiä tai koh-<br>lalle. KEKB-päivityksessä käytettäväksi menetel-<br>entäminen. Tämän seurauksena elektronisuihkun<br>ometrialueelle. Tällä hetkellä mittauslaitteistot eivät<br>minkä vuoksi on kehitettävä uusi laitteisto elektro- |

| Työn tuloksena syntyi toimiva emolevy sekä lait<br>Työssä saavutettiin kaikki emolevylle asetetut va                                                                                                                                                       | teiston vaatimat vahvistin- ja digitalisointipiirilevyt.<br>atimukset.                                                                                                                                                                                                                                                                                                                  |

| paino seuraavan sukupolven laitteen kehitykses<br>kun mittaus yhdessä nopeamman ja tarkemman                                                                                                                                                               | en ja nopeuden suunnittelukriteerit päätetään täs-                                                                                                                                                                                                                                                                                                                                      |

| Avoincenet                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                         |

| Avainsanat<br>STURM2, SuperKEKB, Instrumentation Develop                                                                                                                                                                                                   | ment Laboratory (IDLab), BELLE2                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                         |

## SAVONIA UNIVERSITY OF APPLIED SCIENCES

| Field of Study<br>Technology, (                                                                        | ,<br>Communication and Transport                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Degree Progr<br>Degree Progr<br>Author(s)<br>Jussi Malin                                               | amme<br>amme in Electronic Engineering                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                    |

| Title of Thesis                                                                                        | 3                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                    |

| Motherboard                                                                                            | Design for an X-ray Beam Profile N                                                                                                                                                                                                                                                                     | Monitor System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                    |

| Date                                                                                                   | 3 April 2012                                                                                                                                                                                                                                                                                           | Pages/Appendices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50/45                                                                                                                              |

| Applied Scien                                                                                          | ner, University Hawaii at manoa, S<br>ices                                                                                                                                                                                                                                                             | Senior teacher Ari Suope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | elto, Savonia University of                                                                                                        |

| Project/Partne<br>University Ha                                                                        | ers<br>waii at manoa, Instrumentation Dev                                                                                                                                                                                                                                                              | elopment Laboratory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                    |

| Abstract                                                                                               | of this thesis was to develop a moth                                                                                                                                                                                                                                                                   | porboard for a 64 channe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | l v-ray beam profile moni-                                                                                                         |

| tor system. The<br>collider's elect<br>reliable and he<br>ment of the m                                | the x-ray monitor system is used for<br>tron beam. The goal was to design<br>igh speed measurement and digita<br>notherboard was done at the Instrum<br>noa using the PADS circuit board de                                                                                                            | measuring a beam profil<br>and manufacture circuit<br>Ilization of the x-ray bean<br>nentation Development L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | e and alignment of the<br>boards that would allow<br>n profile. The develop-                                                       |

| main goal of t<br>than the origin<br>beam cross s<br>is changing th<br>micrometer to<br>ment of the el | art of the Japanese KEKB - electron<br>he upgrade is to increase the lumin<br>hal value. This can be done by eithe<br>ection, therefore making the beam<br>he density of the beam. This means<br>a nanometer scale. Present device<br>ectron beam cannot detect nanometer<br>t device is needed.       | osity of the collider to a verification of the collider to a verification of the beam in more dense. The method that the cross section of the used to measure the less used to measure the less section of the section o | value 20 times higher<br>itensity, or reducing the<br>d used to upgrade KEKB<br>the beam reduces from a<br>beam profile and align- |

| boards neede<br>Further devel-<br>will double the<br>device will be<br>with faster an<br>The desired n | fully functioning motherboard was r<br>ed for the device. The motherboard<br>opment of the monitoring system wi<br>e amount of measurement channels<br>to achieve faster measurement wit<br>d more accurate AD conversion.<br>nonitoring accuracy and speed alon<br>ence and performance of the 64-cha | reached all of its design<br>ill be a 128-channel devic<br>s. The focus on the next of<br>h more samples from each<br>ng with other design criter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | criteria.<br>ce, which<br>generation measuring<br>ch electron bunch, along                                                         |

| Keywords<br>STURM2, Su                                                                                 | perKEKB, Instrumentation Develop                                                                                                                                                                                                                                                                       | ment laboratory (IDLab),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BELLE2                                                                                                                             |

## **Table of contents**

| 1  | Introduction                               | 8  |

|----|--------------------------------------------|----|

| 2  | Device performance criteria                | 10 |

| 3  | Amplifier board                            | 13 |

|    | 3.1 Amplifier board assembly               | 15 |

|    | 3.2 Amplifier board testing                | 16 |

| 4  | ASIC board                                 | 20 |

| 5  | STURM2 ASIC                                | 21 |

|    | 5.1 Sampling                               | 21 |

|    | 5.2 Digitalization                         | 22 |

| 6  | STURM2 Firmware                            | 24 |

| 7  | Fermionics sensor                          | 27 |

| 8  | Motherboard                                | 31 |

|    | 8.1 Motherboard design rules               | 32 |

|    | 8.2 Component placing                      | 34 |

|    | 8.3 Power planes and plane areas           | 35 |

|    | 8.4 Analog signal routing                  | 38 |

|    | 8.5 Digital signal routing                 | 40 |

|    | 8.6 Finalized board                        | 43 |

| 9  | Hardware testing and verification criteria | 44 |

|    | 9.1 Testing phase 1                        | 44 |

|    | 9.2 Testing phase 2                        | 44 |

| 10 | ) Conclusions                              | 46 |

| 11 | Lessons learnt                             | 47 |

| 12 | 2 Further development                      | 48 |

| 13 | Symbols, terms and abbreviations           | 49 |

| Re | eferences                                  | 50 |

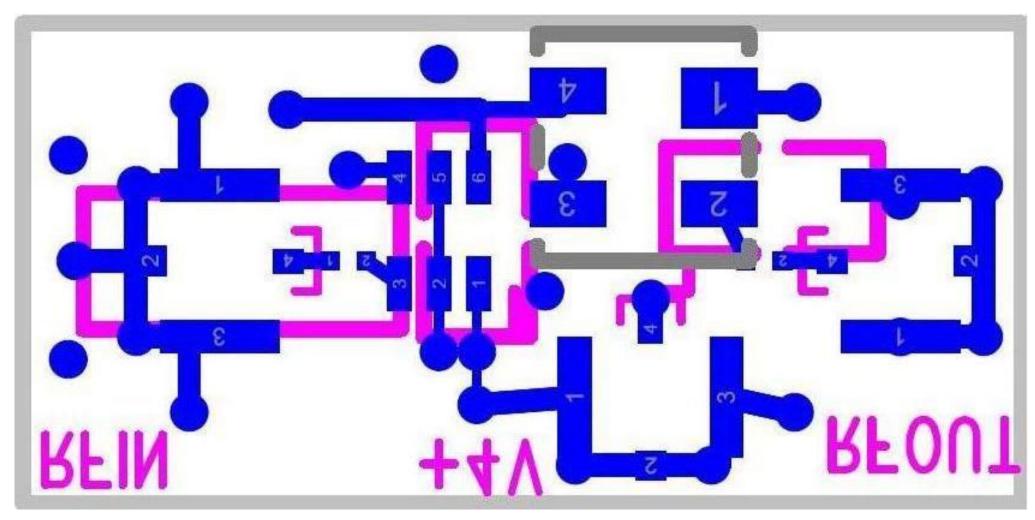

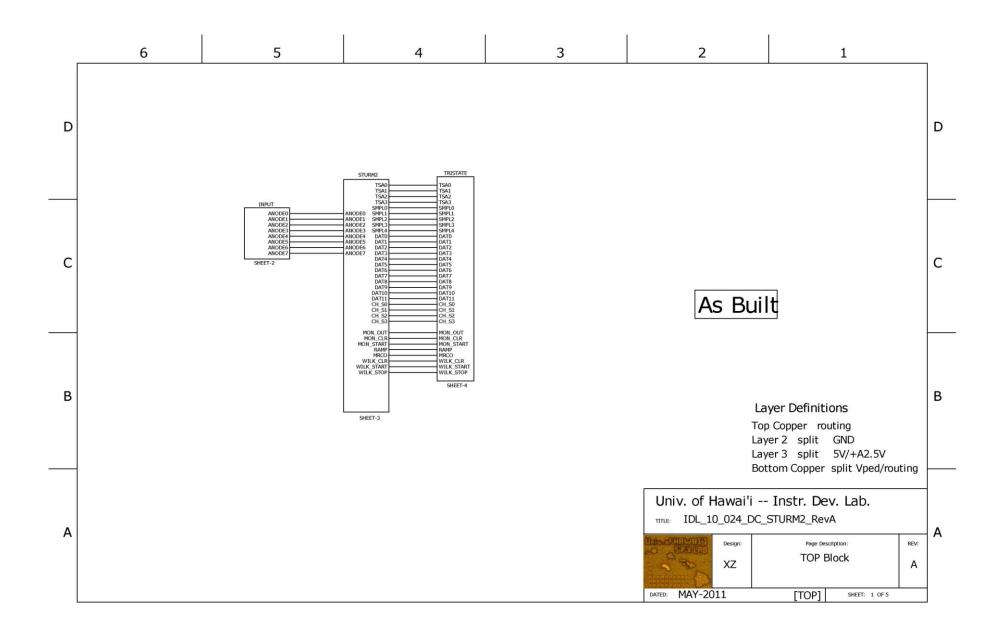

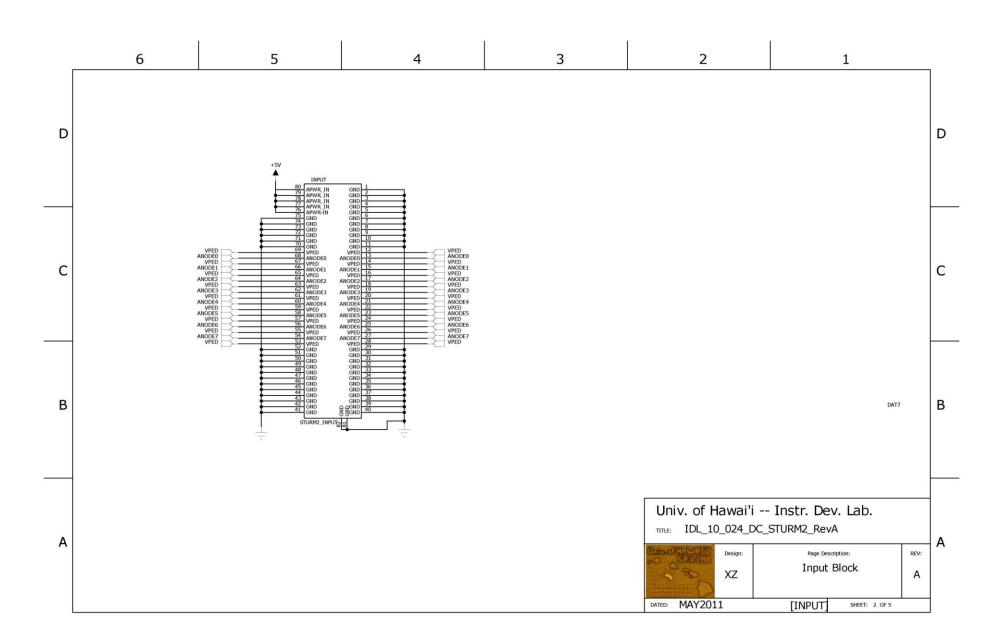

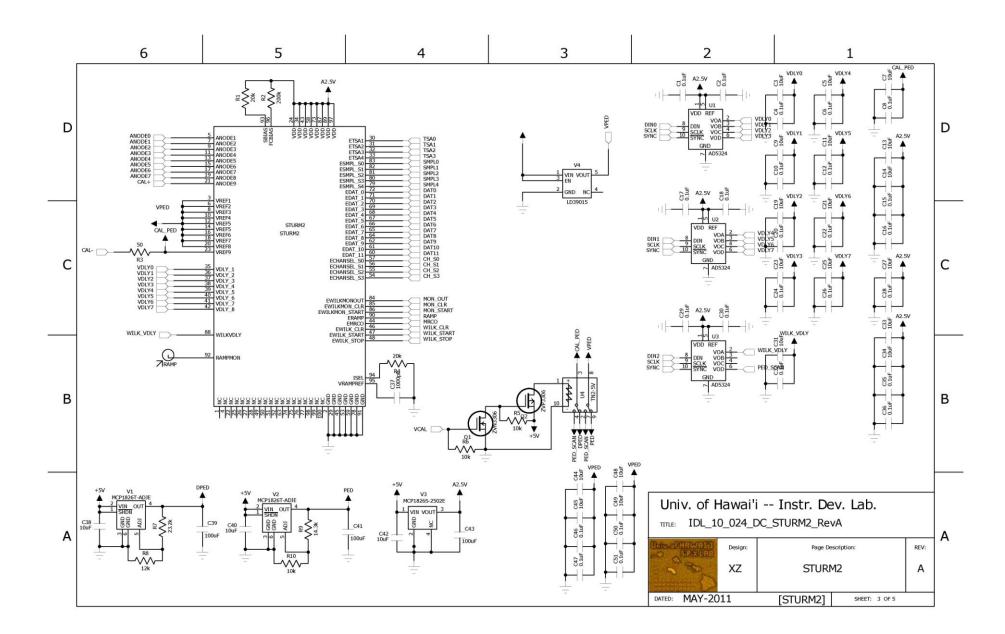

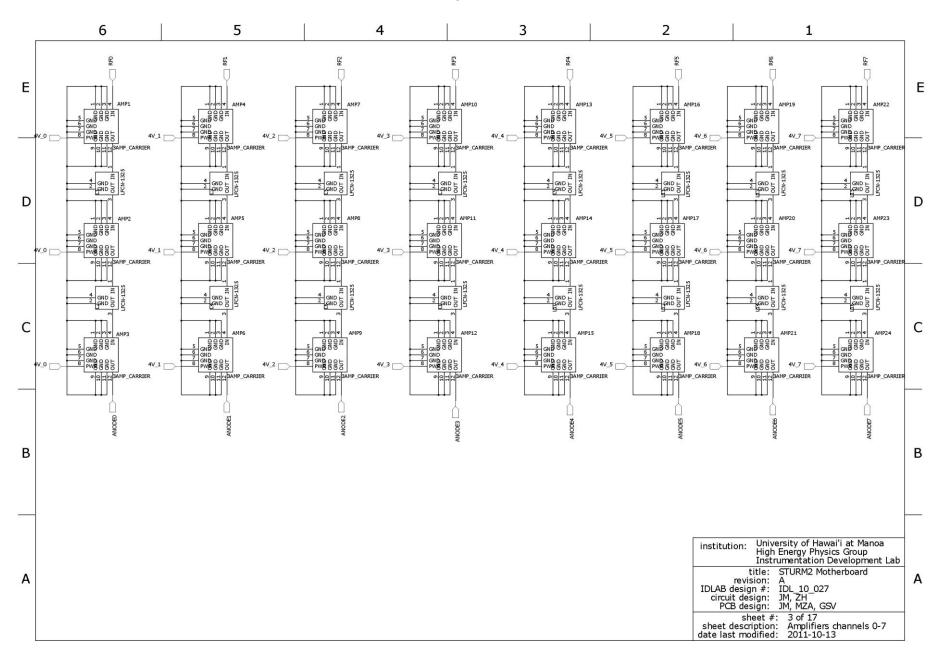

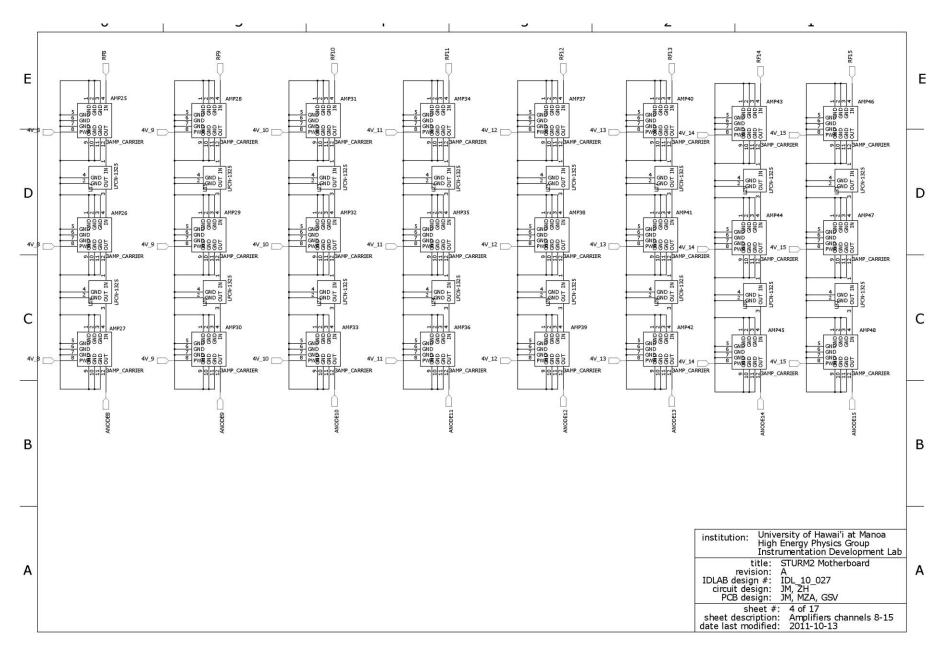

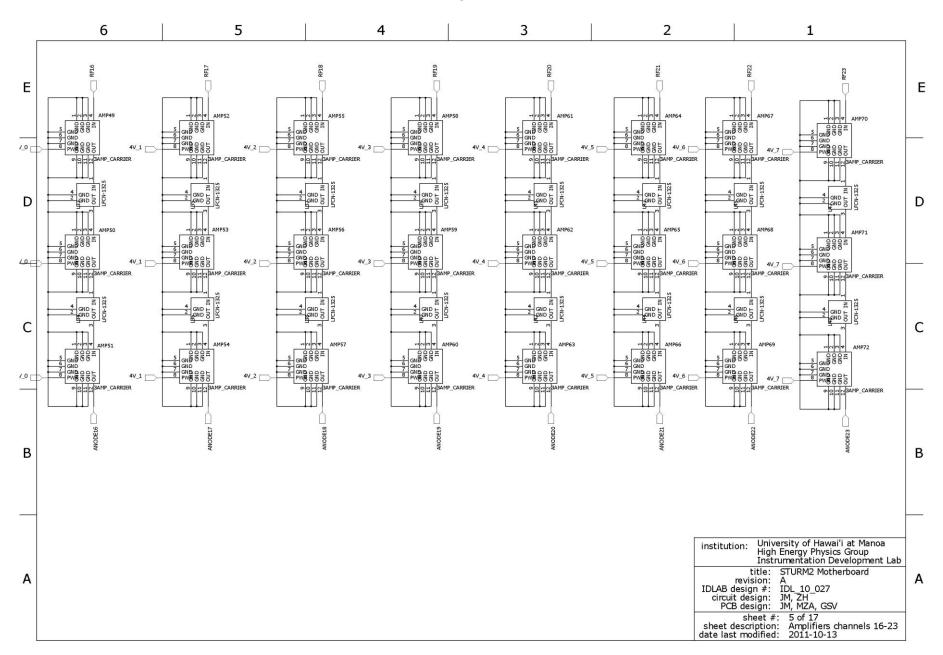

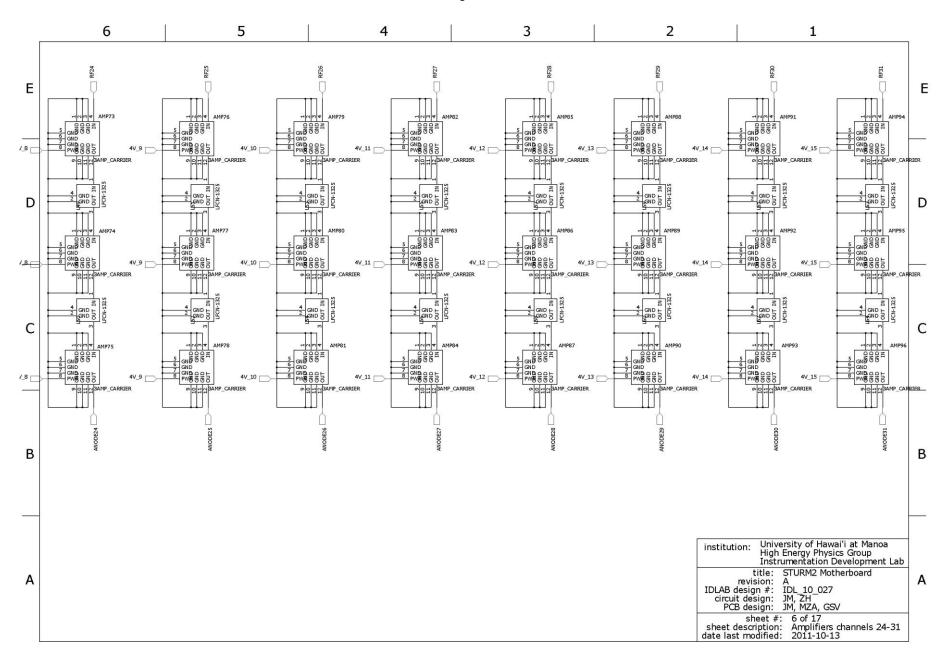

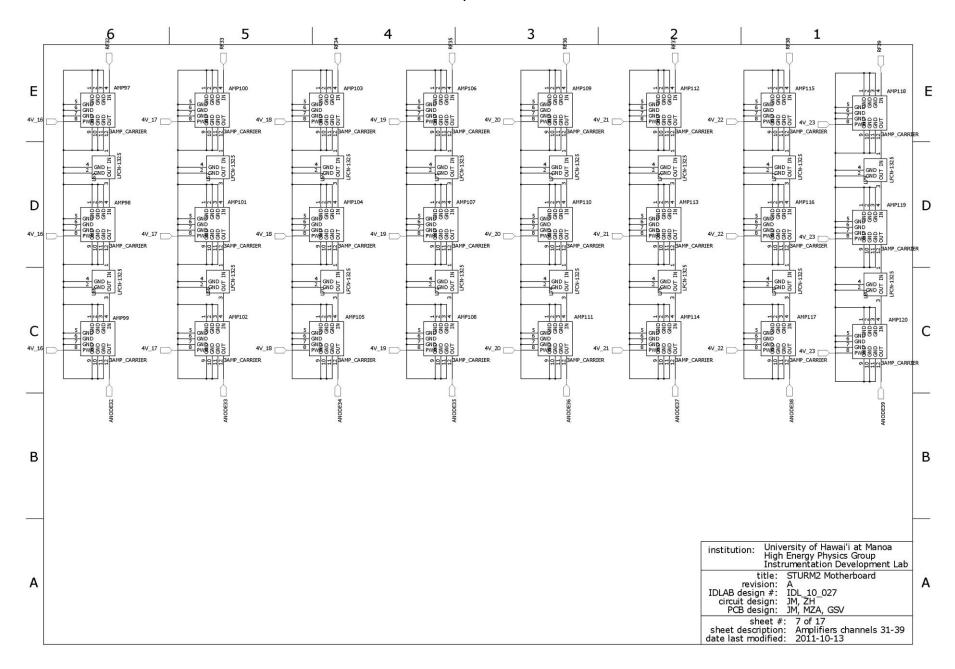

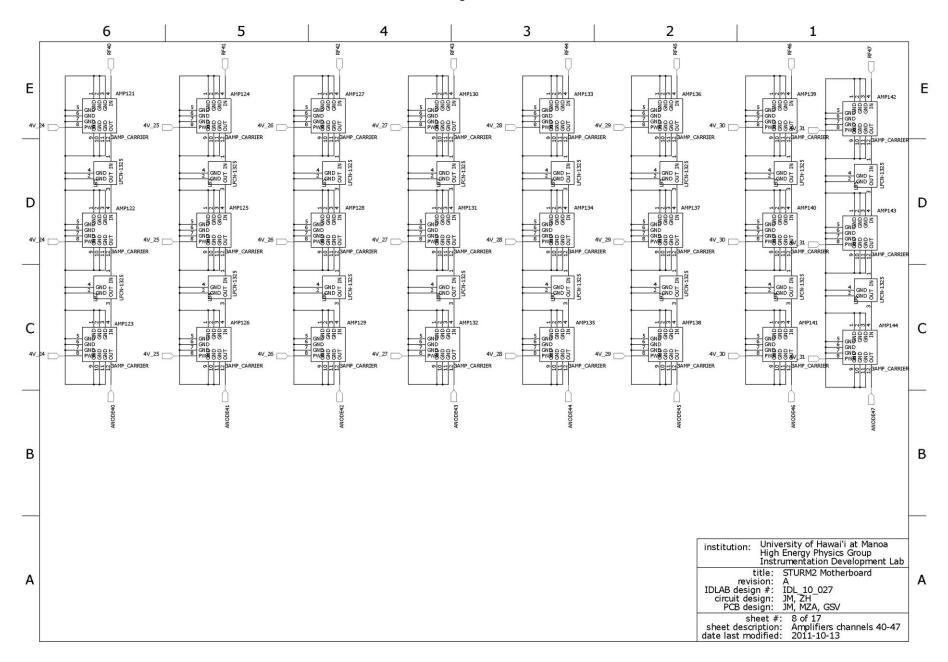

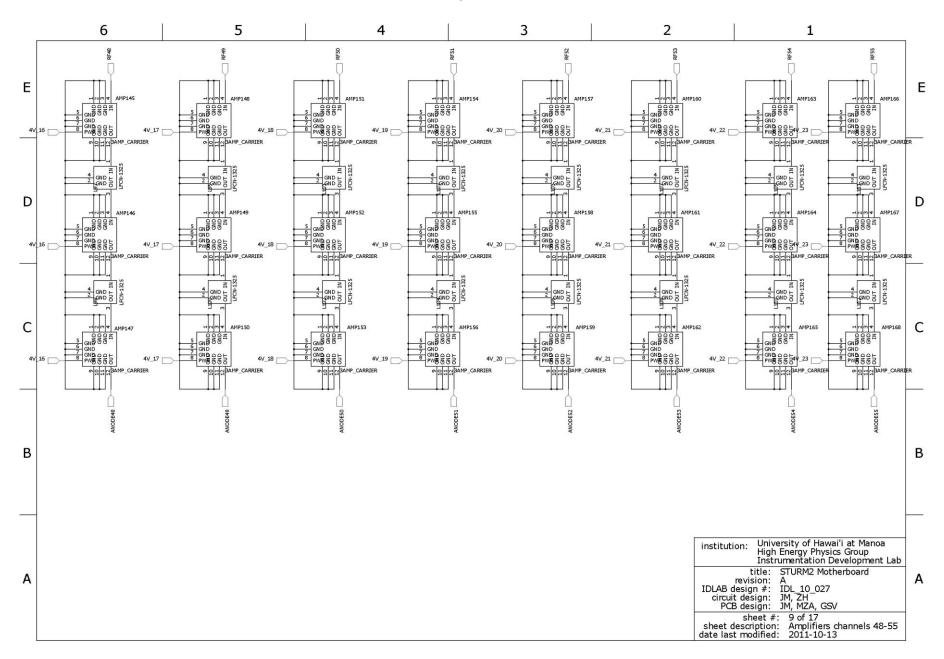

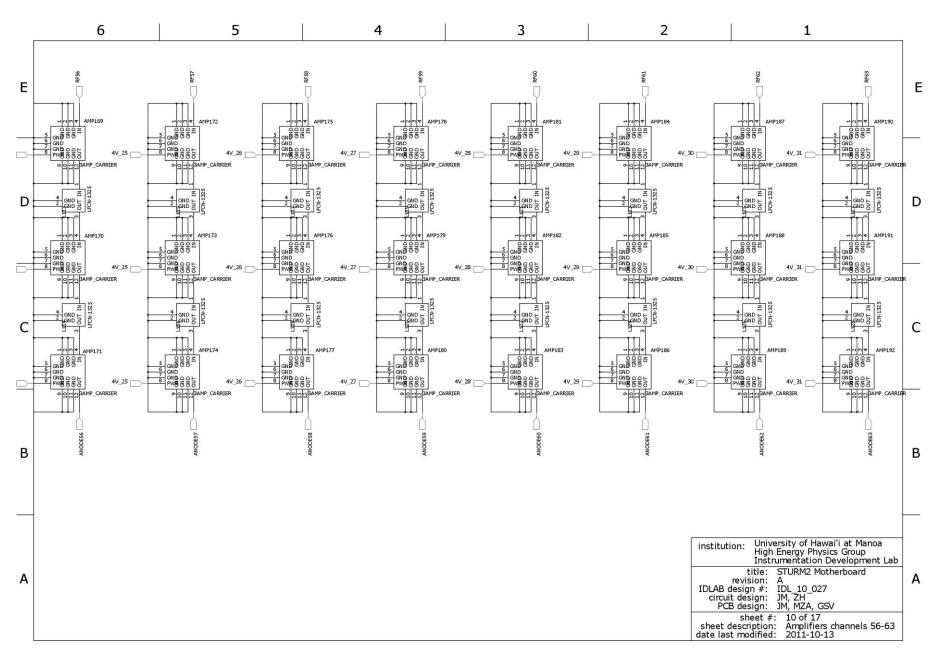

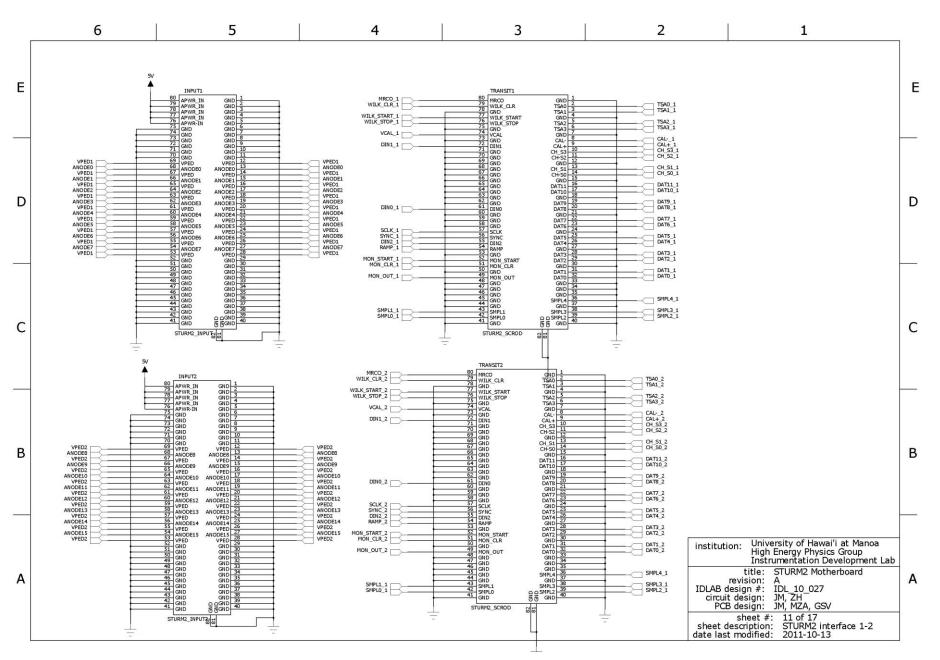

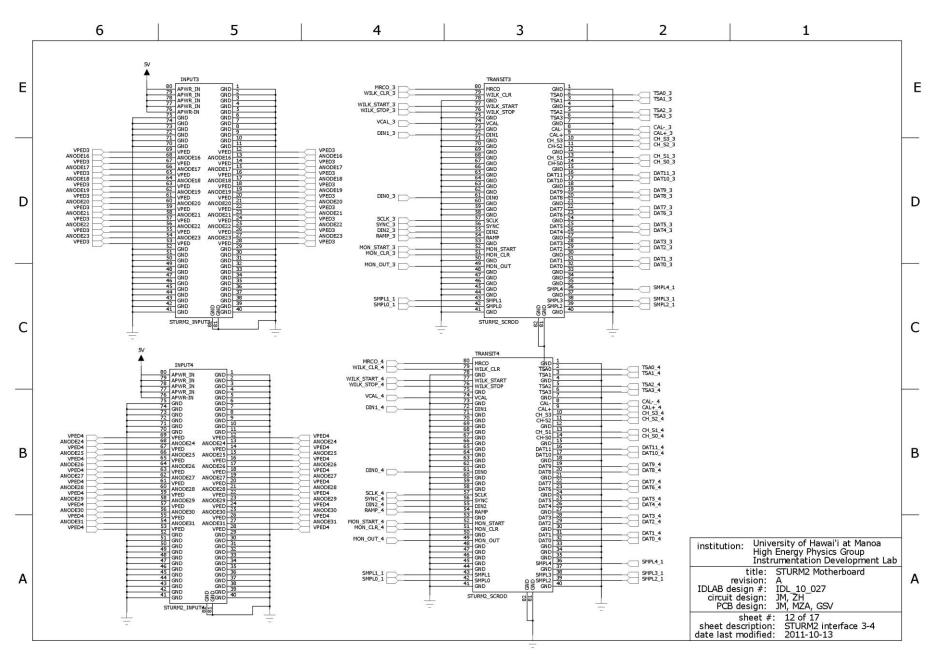

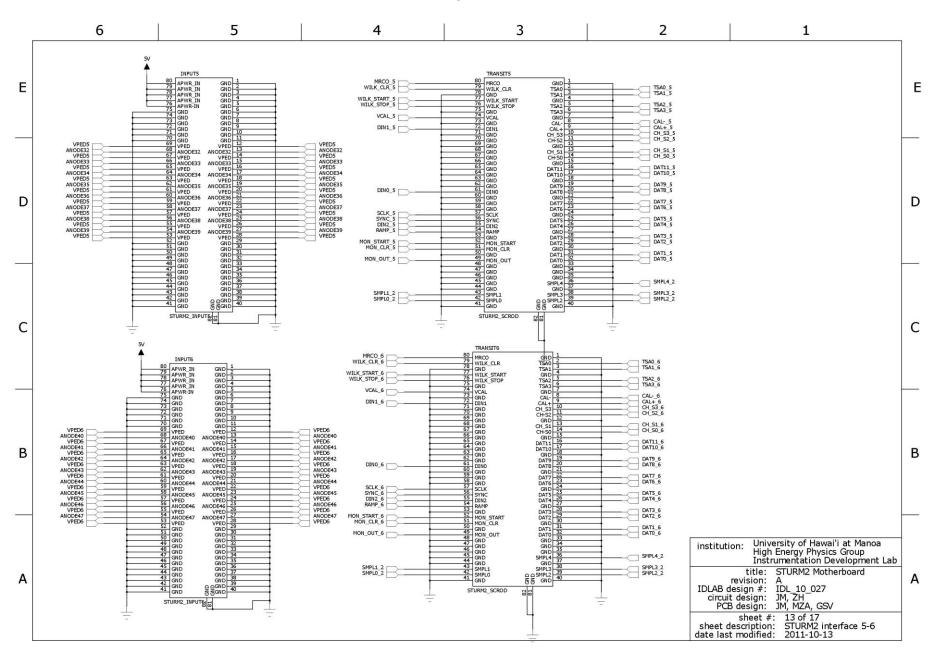

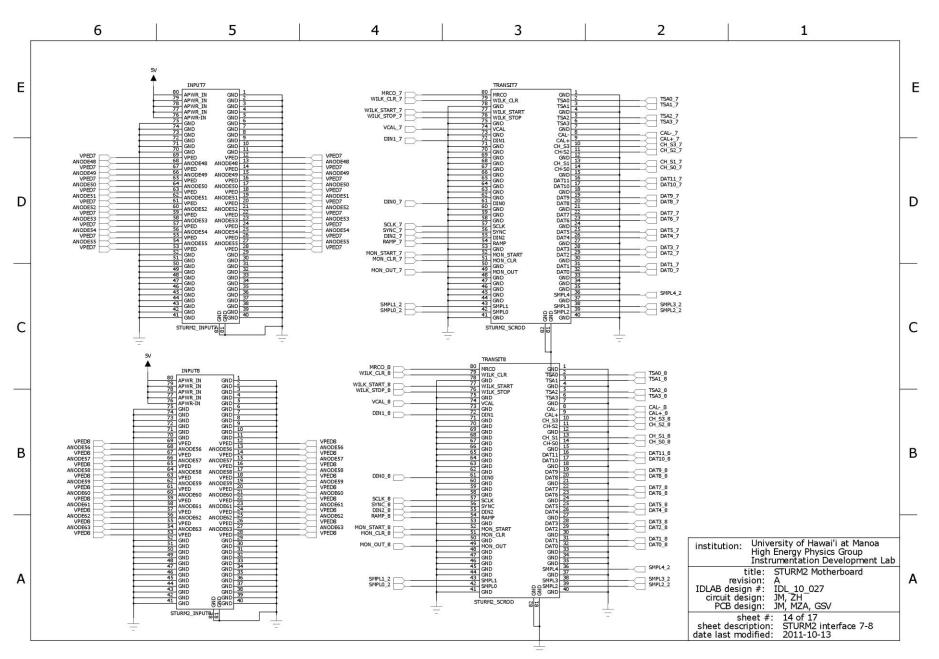

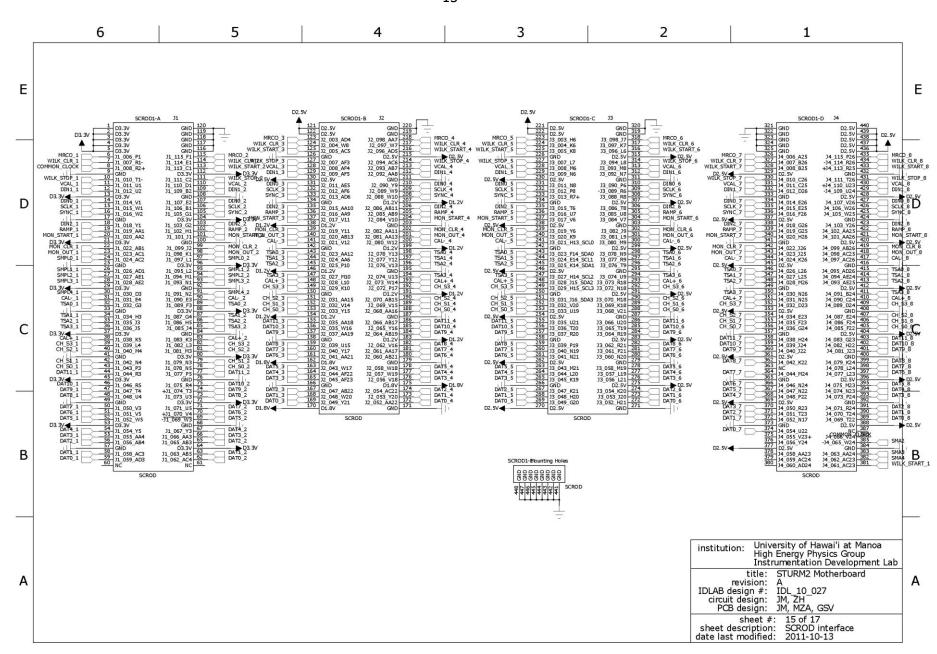

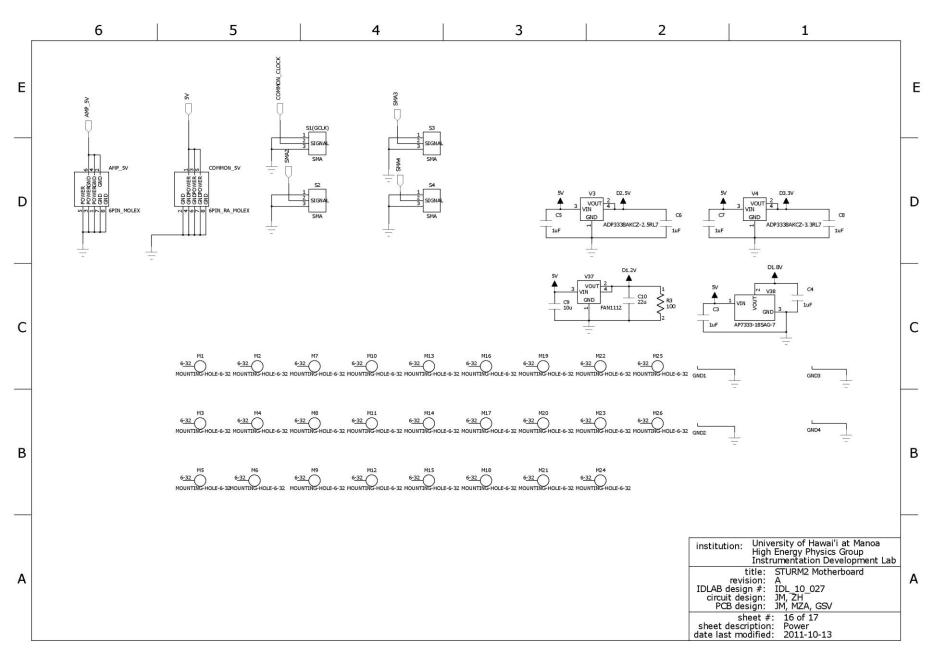

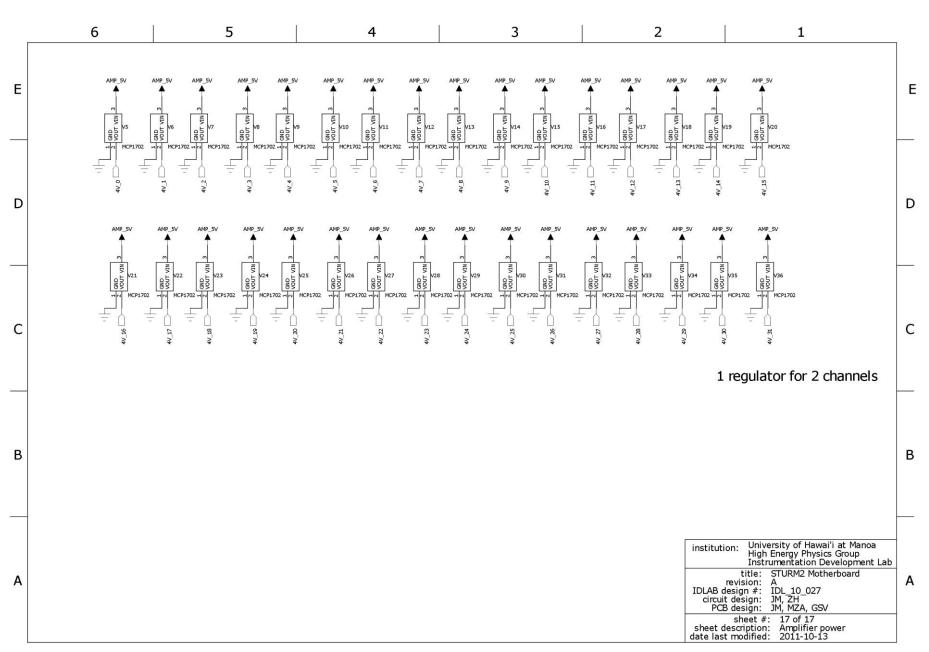

#### Appendixes

- Appendix 1 STURM2 amplifier board revision C schematic Appendix 2 STURM2 amplifier board revision C layout Appendix 3 STURM2 ASIC board revision B schematic Appendix 4 STURM2 ASIC board revision B layout Appendix 5 STURM2 motherboard revision A schematic Appendix 6 STURM2 motherboard revision A layout Appendix 7 CPG18020 datasheet

- Appendix 8 STURM2 bill of materials

#### Forewords

This thesis was done for the Instrumentation Development Laboratory at University of Hawaii. During this thesis I learned a great deal of new skills in the field of electronics engineering, as well as improved my existing skills to a higher level. The experience gained from working on an international project and workgroup as well as the improved skills in English will most definitely serve me well in my future career.

I would like to thank Dr. Gary S. Varner for providing this great opportunity for the thesis, and for his guidance during the exchange period.

I would like to address my thanks to my supervisor Ari Suopelto for his feedback and support.

Kuopio 2012

Jussi Malin

## 1 Introduction

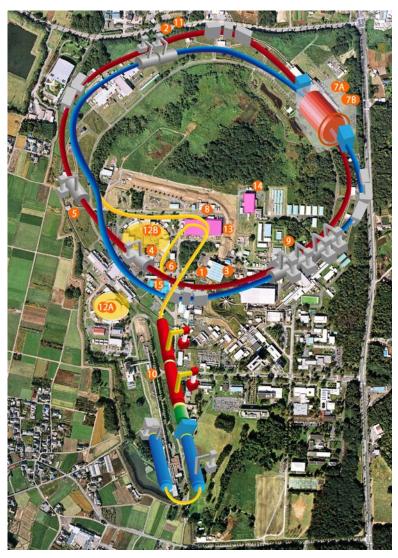

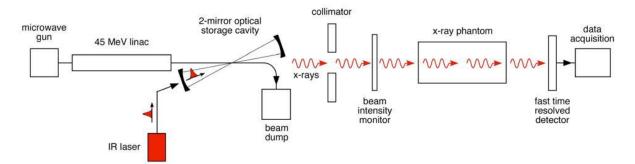

STURM stands for Sampler of Transients for the Uniformly Redundant x-ray Mask. This project has it's origin in upgrading the KEKB electron-positron collider, shown in Figure 1, at the KEK High Energy Physics Laboratory in Tsukuba Japan to Super-KEKB. When the upgrade is finished, the Super-KEKB will have the world's highest luminosity. This higher luminosity is needed for the upgraded BELLE2 detector, which is used to measure charge-parity violations. The upgrades will allow this experiment to continue with much higher precisions. The BELLE2 detector is located at 7A in Figure 1. The STURM2 measuring device will be installed at close proximity of the point 7B in Figure 1, which is the location of the quadruple superconducting magnet and also the point of collision.

FIGURE 1. KEKB facilities and components. Picture High Energy Accelerator Research Organization, (KEK) 2012

At the Super-KEKB collider, the beams will be squeezed to nanometre scale. Therefore, the previous measuring devices can no longer track the beam at the collision point. Without reliable tracking and monitoring equipment it is impossible to collide the beams with proper accuracy. Also, the collision of the beams will not always happen head on. Depending on the experiment, the beam bunches will be driven together with an 1 to 5 degree angle. The STURM2 can measure the location, profile and angle of the beam right before the collision point, allowing the physicist to adjust the beam as he desires. When implemented, the STURM2 device will be the most accurate real-time, turn-by-turn monitoring system. (High Energy Accelerator Research Organization, KEK).

#### 2 Device performance criteria

The STURM2 monitoring device consists of three key components. A fast fermionics sensor with RF amplification, a 10 to 100 Giga-samples per second digitizer, and a fast acquisition back-end transmitting the data to the main control room. Before setting out to design any of the components, it is crucial to understand the design criteria for all the devices. Before any of the design work was started, the most critical values were calculated. In the Super-KEKB, the most important values are the available time for the measurement, and the amplification needed for the RF signal.

In the Super KEKB collider, the electron bunch travels nearly at the speed of light, which will set a high demand for the measuring speed. In addition, the distance where the sensor can pick up the X-ray beams, is only 5 millimetres. The time T available for the measurement can be found in equation 1.1.

$$T = \frac{L}{V} = \frac{5,00*10^{-3} m}{2,99*10^8 m/s} = 16,72 \ pS$$

[1.1]

Where

L is the length of the fermionics sensor V is the light speed constant

To calculate the needed amplification to reach the desired output voltage, the sensor's own output voltage must be solved first. The energy of the electron beam at Super-KEKB collider can reach 4 KeV, meaning that the most energetic x-ray beam can also reach 4 KeV. Depending on the angle of the beam when it passes the sensor, the estimated energy of the beam varies between 2 to 4 KeV. For these calculations, the energy of the x-ray beam was assumed to be 3.6 KeV, which is well between the possible fluctuation.

When the x-ray beams hit the surface of the sensor arrays, they release electron – hole pairs. With the material used in the fermionics sensor, 3.6 electron volts is needed to release one pair. Therefore, 3.6 KeV will release 1,000 electron – hole pairs. (STURM-based x-ray Monitor Meeting page)

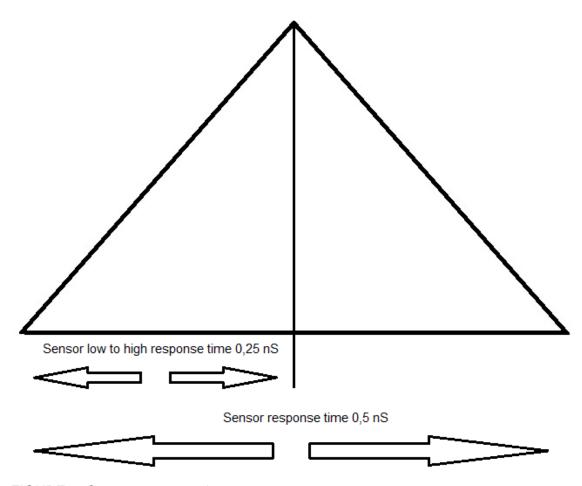

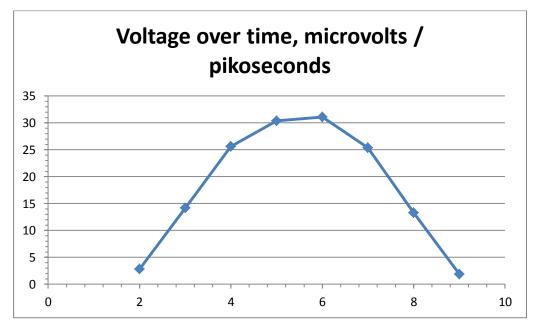

Now the sensor's response time must be taken into account to solve the sensor output current, in order to solve the output voltage. The sensor used in this device has a low-high response time of 0.25 nS as can be seen in Figure 2. When signal intensity changes, the sensors output current changes accordingly. The change from low- to high and high- to low is identical, so the current change  $\Delta I$  has to be calculated in only one case.

FIGURE 2. Sensor response time.

One electron – hole pair has the charge of 0.16 attocoulomb, Therefore 1,000 pairs will have the charge of 0.16 femtocoulomb. The coulomb is defined by ampere in seconds, so change in amperes  $\Delta I$  can be solved with equation 1.2. (STURM-based x-ray Monitor Meeting page)

$$\Delta I = \frac{\Delta C}{\Delta t} = \frac{1000i}{2.5*10^{-10}S} = \frac{0.16*10^{-15}C}{2.5*10^{-10}S} = 0.64 \ \mu A$$

[1.2]

Before setting out to do the design work, the impedance of all RF transfer lines was set to be 50  $\Omega$ . Several attributes will affect the impedance of the transfer line, including trace width, height, thickness and the relative permittivity of the dielectric. The impedance fitting was done by changing the trace width, which is the easiest and most cost efficient way. The trace width calculations were done by online calculation software, provided by the PCB manufacturer.

Using Ohm's law, the voltage change  $\Delta V$  in the 50  $\Omega$  transfer can be solved with equation 1.3.

$$\Delta V = \Delta I * R = 0.64 * 10^{-6}A * 50 \ \Omega = 32 \ \mu V$$

[1.3]

The 32 microvolt output voltage is too small for accurate measurements. A voltage this small will be lost in the background noise, corrupting the results. Prior to any design work, an output voltage of 10 millivolts was chosen to be an adequate voltage level. The amplification G needed can be solved with equation 1.4

$$G = 20 * Log_{10} \frac{U_{out}}{U_{in}} = 20 * Log_{10} \frac{10 * 10^{-3} V}{32 * 10^{-6} V} = 49,89 \ dB \approx 50 \ dB$$

[1.4]

Instead of using one massive amplifier, the amplification was broken into three stages. By doing the amplification in three stages it is possible to remove possible interferences from the signal by placing necessary filters between the amplifiers. Also a design of 20 dB amplifier is less complex than designing a 60 dB amplifier, and can be done in a much shorter timeframe. (STURM-based x-ray Monitor Meeting page)

#### 3 Amplifier board

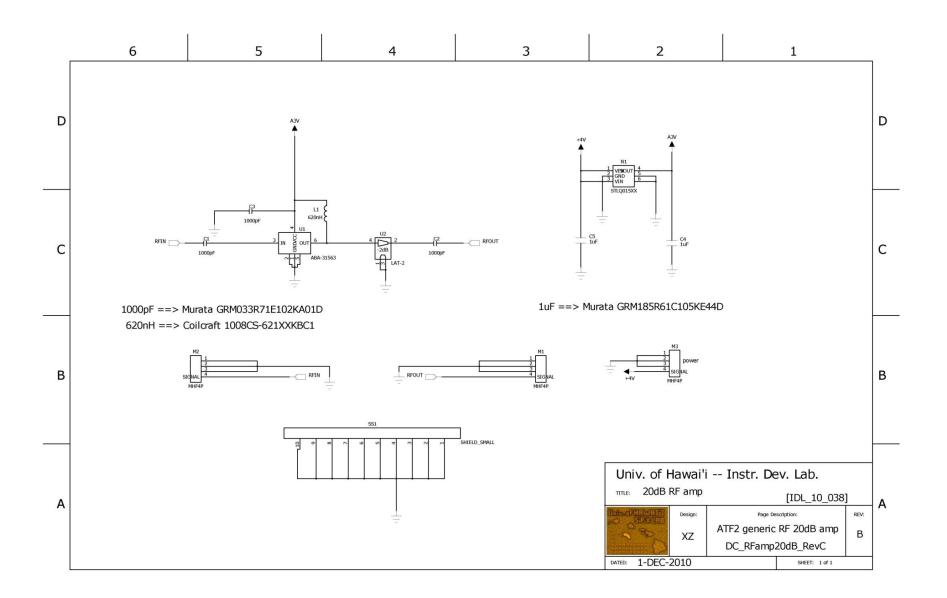

The STURM2 device holds three amplifiers for each of the 64 channels, a 192 amplifiers altogether. The amplifier board's function is to perform a 20 dB amplification to the sensors RF signal. The amplifier is located on its own circuit board, and it will be plugged in to the STURM2 motherboard. This method has several benefits compared to that if the amplifiers would be physically located on the motherboard. This method makes it possible to change individual amplifiers in case of amplifier failure. In future, if a new version of the amplifier is created with more advanced components, it is very easy to upgrade the device. It is also possible to test individual amplifiers, and remove those boards that do not meet their performance criteria before they are plugged in.

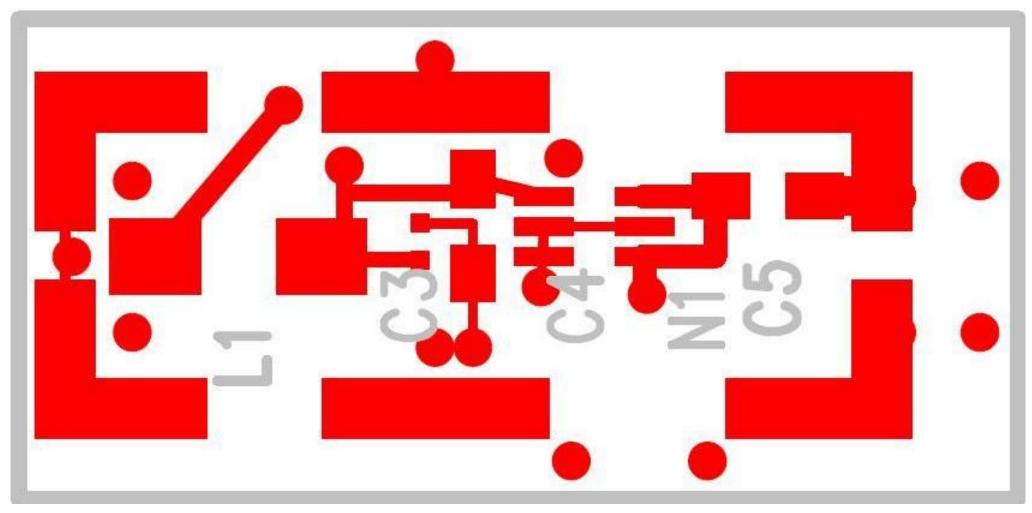

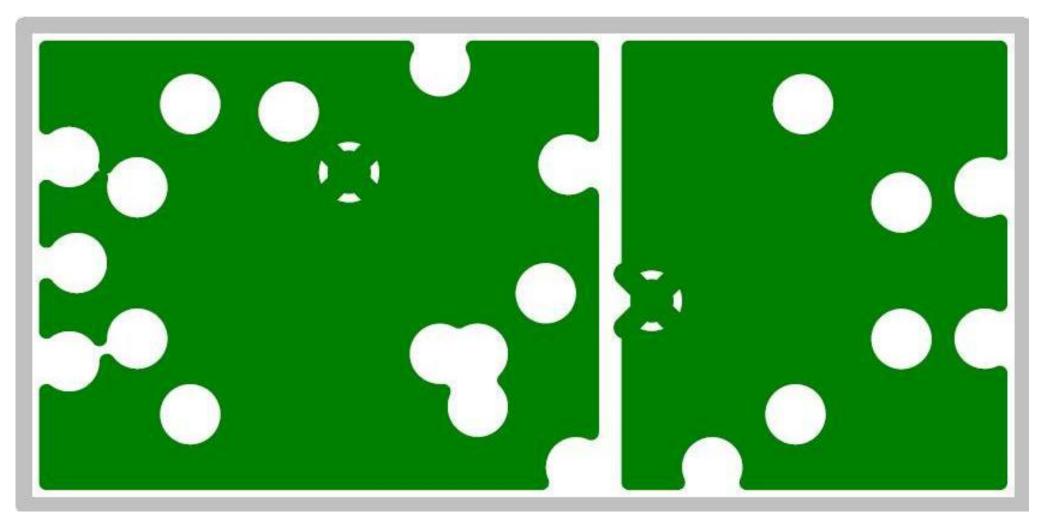

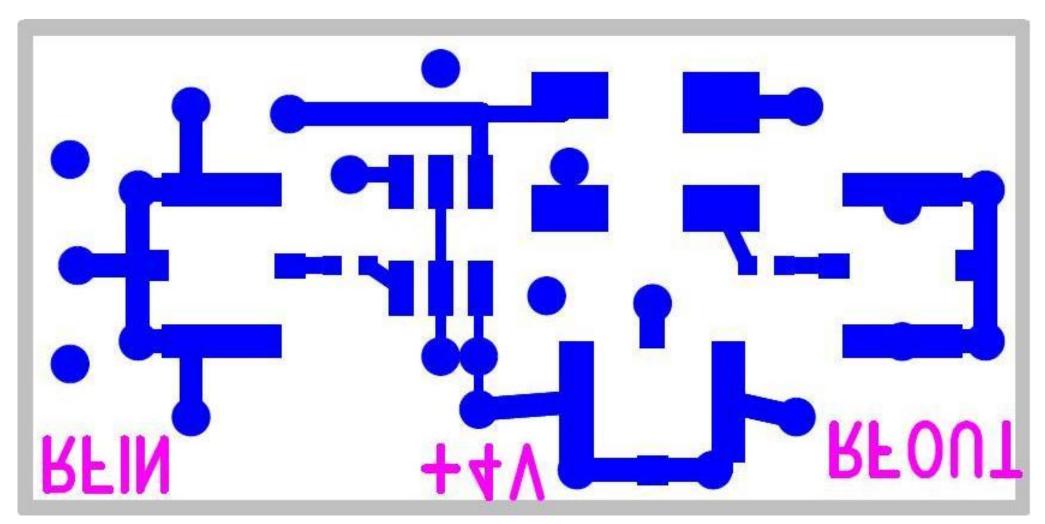

The amplifier board consists of four planes. Primary component plane, power plane, ground plane and RF component plane. These are shown in appendix 2. Along with the amplifier board, another board was also made for testing purposes, called the carrier board.

The carrier board has the same type of connectors as the motherboard will eventually have, and the amplifier board can be plugged into it for performance testing. The benefit of having a carrier board is that the testing of the amplifier design can begin at earlier stages of the project. Carrier boards only function is to provide SMA connectors for the amplifier boards RF input and output signal, and for amplifier board power connector.

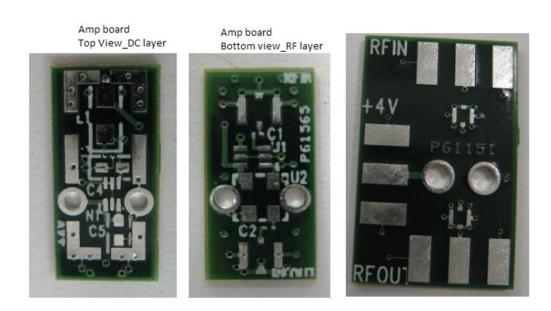

The first version of the board used a single connector for the RF input and output and power. This design never reached the design criteria. In the second version of the board, the RF connectors were replaced with solid steel splinters, and the board was connected by soldering these splinters to make a permanent joint. The solder applied by hand caused interferences in the transfer line, and this design was scrubbed as well. The second version of amplifier board is shown in Figure 3, along with the corresponding carrier board. (STURM-based x-ray Monitor Meeting page)

FIGURE 3. Amplifier board version 2. Picture Xi Zhao 2011

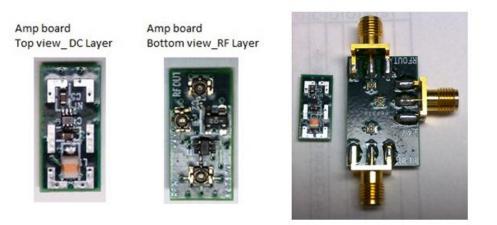

The amplifier board used in the device is the third design version. There were two main issues which made the amplifier board design challenging. The frequency of incoming RF signal is over 2 GHz. This combined with the fact that the board has to connect to another board with RF connector caused the main issues. To minimize signal losses, the transfer lines were designed as short as possible throughout the whole device. This meant that the RF connectors used to connect the amplifier board to the motherboard had to have the same impedance as the transfer lines, and to minimize further losses, they needed to be as small as possible. The third version of the amplifier board is shown in Figure 4 along with the corresponding carrier board. (STURM-based x-ray Monitor Meeting page )

FIGURE 4. Final version of the STURM2 amplifier board and carrier board.

#### 3.1 Amplifier board assembly

The small RF connectors, highlighted in Figure 5, on the amplifier and carrier board made assembly of the boards very difficult. The copper pads on both of the boards are significantly larger than the legs of the RF connector. This means that placement of the RF connector can vary a lot, while it is still within the borders of the copper pad on the circuit board. Alignment of all of the three RF connectors turned out to be a major issue, especially when the tolerances in the RF connector are less than a millimeter.

FIGURE 5. RF connectors on the carrier board

Before placing a large order of all the amplifiers, three amplifiers were assembled by hand for testing purposes. The alignment of the RF connectors took several attempts, and the final placement still was not satisfactory. This problem was solved by following method: The connectors on the carrier board were soldered first, and the amplifier board connectors were attached to connectors on the carrier board. Then a small amount of flux was placed on the bottom side of the amplifier board connectors, which were now facing upwards.

The amplifier board was then pressed against the upward facing connectors carefully under microscope. Now the flux on the connectors left marks on the amplifier board copper pads. Using this flux marks it was possible to solder the RF connectors on the amplifier board to proper place. This kind of method is only good for assembling a few boards, since it is very slow and not accurate method. As a result, one amplifier board only connected properly to one specific carrier board. As a mass production phase, this alignment will be done with proper equipment by a local company where the board assembly is done.

#### 3.2 Amplifier board testing

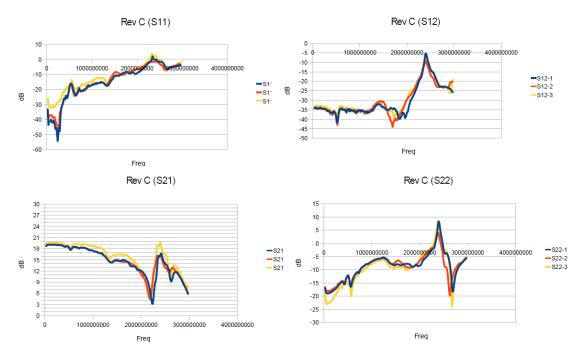

Testing of the board performance was done using a network analyzer. The network analyzer measures four signal parameters, known as S-parameters. The parameters are split to transmission and reflection. The two transmission parameters tell how much the signal strength changes, and the reflection parameters tell the reflection that happens between the devices input and output port. The Parameters are marked [S21], [S12], [S11], [S22]. In the S-parameters the first number tells the output port, and the second number tells the input port.

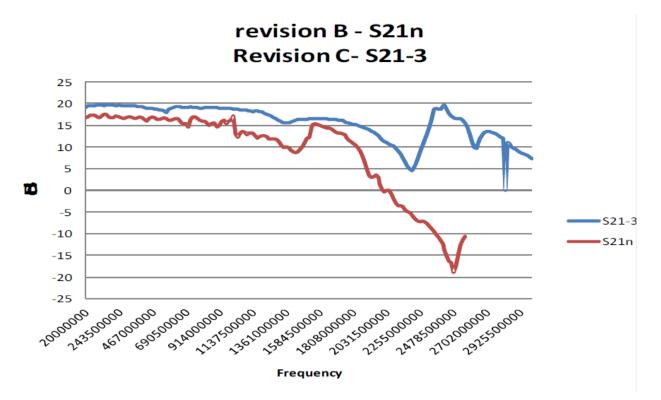

What we are interested in the testing phase is the [S21] parameter that tells how much the signal is amplified when it is fed through the amplifier. This measurement is shown in Figure 6, which also shows the performance of the version 2 amplifier, marked revision B.

FIGURE 6. Amplifier revisions B and C [S21] parameter, amplification.

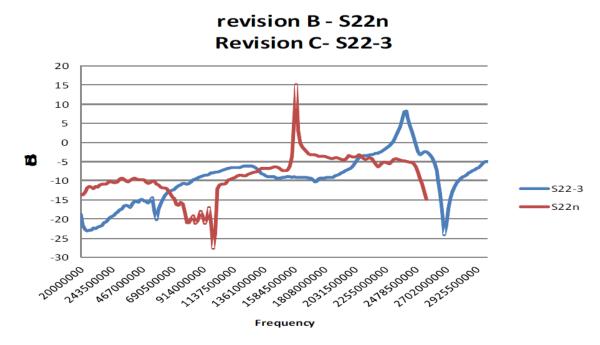

In Figure 6 it can be seen that the revision C amplifier will reach the desired 20 dB amplification up to the frequency of 2.5 GHz. Equation 1.4 shows that total amplification needed is 50 dB, which means that one amplifier only has to reach 16.6 dB. However, at 2.5 GHz the amplification drops dramatically. This is caused by the reflection in the output port, parameter [S22] shown in Figure 7. At 2.5 GHz nearly 10 dB of the signal strength is reflected back.

FIGURE 7. Amplifier revisions B and C [S22] parameter, reflection at output port.

Figures 6 and 7 show that amplitude of the reflection matches the drop in the signal output. The performance can be improved by adding a low pass filter to the mother-board between the amplifier stages. The low pass filter will eliminate the reflection spike therefore improving the amplifier performance. This low pass filter for the design was chosen by Dr Gary S Varner. More details about the low pass filter can be found in Appendix 5, pages 3 - 8.

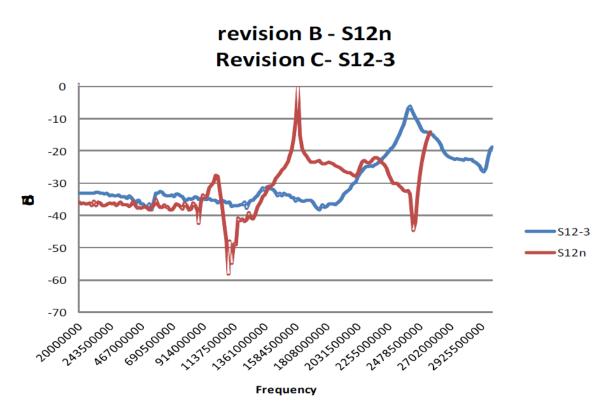

The other remaining parameters are [S12], which tells the change in the signal strength from output to the input port, and [S11], which tells the reflection at the input port. Figure 8 shows that the [S12] parameter is negative. This is because the output signal is much greater than the input. The attenuation in the [S12] is greater than the amplification in the [S21]. This is because all the signal losses in the amplifier board components are also added to the [S12]. In an ideal device, the amplification of the [S21] would be the same as the attenuation of the [S12].

FIGURE 8. Amplifier revisions B and C [S12] parameter, signal strength change from output to input.

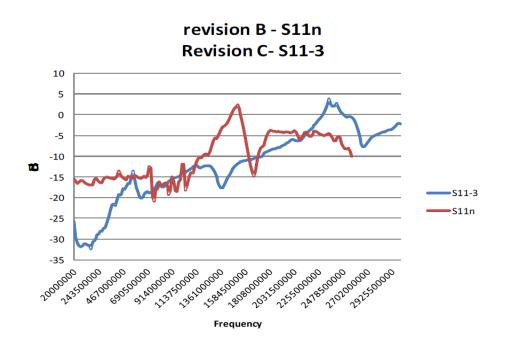

Figure 9 shows the reflection in the amplifier board input port. Again a spike appears between 2.25 GHz and 2.5 GHz. This can be also eliminated with a properly matched low pass filter.

FIGURE 9. Amplifier revisions B and C [S11] parameter, reflection at the input port.

The final phase of amplifier testing is to make sure that all three amplifiers have the same performance. If one of the amplifiers is not performing adequately, the whole amplifier stage is affected, and the results from that RF signal line are corrupted. The three amplifiers assembled by hand and tested individually, and the testing results were plotted into same graph. Figure 10 shows the testing results of these three amplifiers.

FIGURE 10. Amplifier revision C testing results.

Figure 10 shows that all three amplifiers have a very similar performance. The small differences can be assumed to be caused by the method of how the RF connectors were aligned and soldered. When using proper machinery at the manufacturing process, these differences will be significantly smaller.

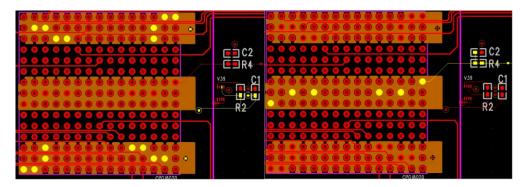

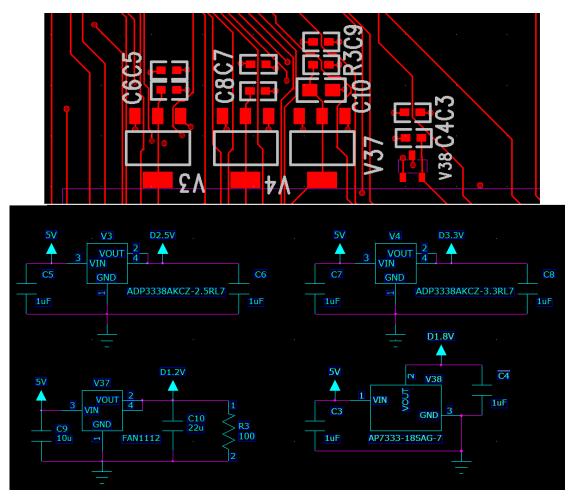

## 4 ASIC board

After the amplifier stage, the signal is fed to the ASIC board. The main function of the ASIC board is to house the STURM2 ASIC chip, provide its operating voltages and supporting devices, and to connect the signal line to the acquisition back-end. The ASIC board processes eight RF signals simultaneously, and it is connected to the motherboard with an 80 pin input and output connectors. The board has four electrical layers, top and bottom for component placing and ground and power as internal layers. The board has two operating voltage levels, 2.5 volts and 5 volts. To ease the routing, the power plane is split into two areas, one for each voltage level, and the components are placed on areas that match their voltages. The schematics and layout of the ASIC board are found in Appendixes 3 and 4.

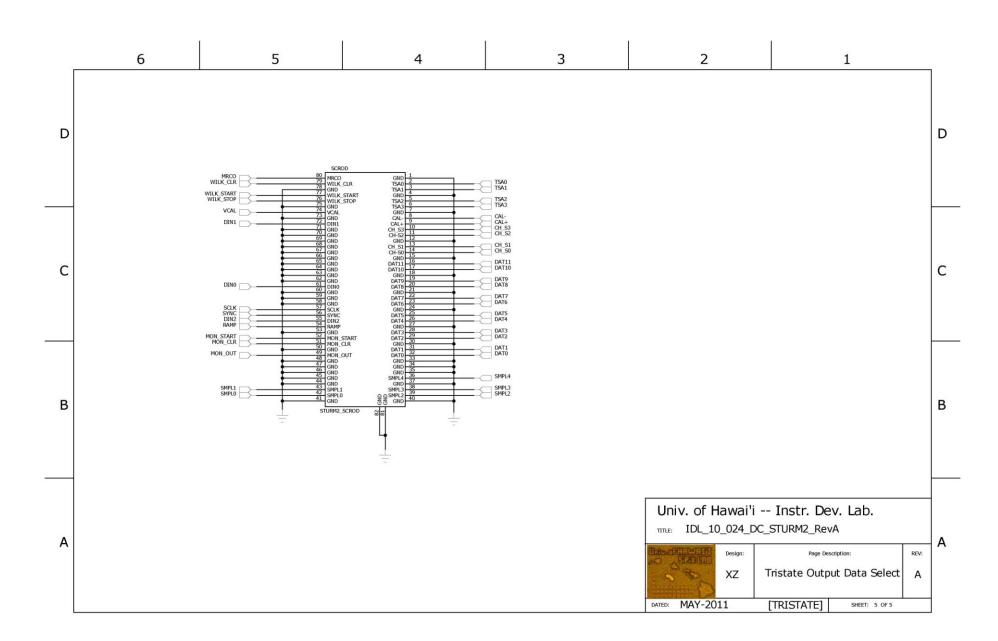

The board's only input signals are the RF signals from the amplifier stages, and power and ground for the components it houses. The signals that are used to control the STURM2 ASIC are controlled through the acquisition back-end, a device known as SCROD. SCROD is device developed earlier in the instrumentation development laboratory. It is used in various projects to provide connection between digital devices such as STURM2 ASIC and a PC environment. The operation of the STURM2 ASIC is covered more deeply in Chapter 6 of this thesis. (STURM-based x-ray Monitor Meeting page)

To test the STURM2 device as whole, one ASIC board was assembled by hand at the Instrumentation Development Laboratory. Already in the assembly phase, several serious flaws in the design were discovered. The footprint of the input and output connector was poorly designed, making the soldering extremely difficult. The most critical flaw in the design was that the distance between these connectors was also improper, and as a result it could not be connected to the motherboard. Two other critical issues concerning component placement were also found. All these flaws put together, it was impossible to properly test the function of the ASIC board. After completion of the main goals of this thesis, a revision B of the ASIC board was made in which all the design flaws were corrected.

## 5 STURM2 ASIC

STURM2 ASIC is a chip designed earlier in the Instrumentation Development Laboratory. The main features of the STURM2 ASIC are following:

- Dimensions 3.3 x 3.3 mm

- 8 input channels

- > 4 x 8 flash samples/channel

- > On chip ADC conversion (~12.5us/256 samples)

Each of the input channels has its own sampling and digitalization circuits built into the chip, so the data of all channels can be processed in parallel. (STURM2 design review, Dr. Gary S. Varner 2009) More detailed information of the STURM2 ASIC signals can be found in Appendix 3.

#### 5.1 Sampling

Each of the channels has 4 flash memory slots, and each of those can hold 8 samples. As the x-ray beam passes through the detector, the measured signal profile is similar to the curve shown in Graph 1. To measure the profile of the x-ray beam, several samples of the signal must be taken.

GRAPH 1. Example of the STURM2 ASIC sampling.

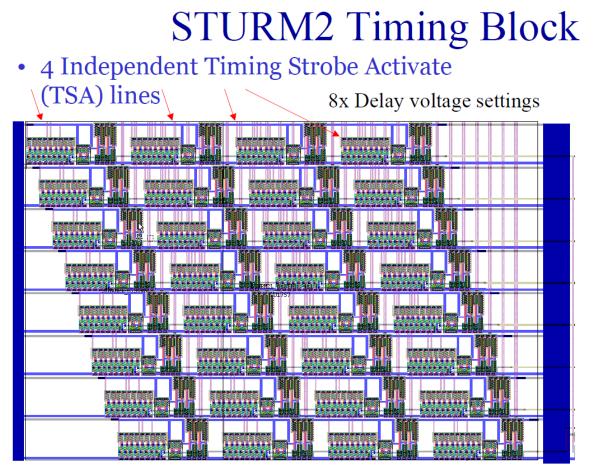

The current STURM2 ASIC version takes eight samples from each channel, and performs a 12-bit AD conversion. The sampling time can be adjusted with four individual TSA lines, which each hold eight voltage delay circuits, shown in Figure 11.

FIGURE 11. STURM2 timing block. Picture Gary Varner 2009

Each of these eight voltage delay circuits can also be adjusted individually with VDLY signals. The physicist using the device can therefore adjust the starting point of the sampling process, and the delay between individual samples.

## 5.2 Digitalization

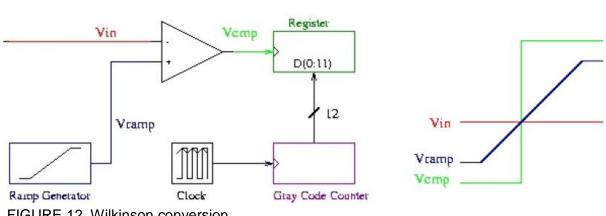

To digitalize the analog signal, STURM2 ASIC uses the Wilkinson conversion, which one great benefit is excellent linearity. The main components needed for the Wilkinson conversion are a comparator, ramp generator, gray code counter, and a clock circuit. The principal of the Wilkinson conversion is shown in Figure 12. (STURM2 design review, Dr. Gary S. Varner 2009)

23

FIGURE 12. Wilkinson conversion.

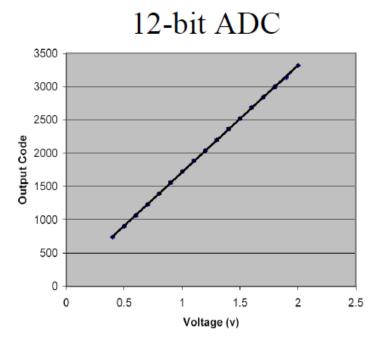

When the conversion is started, the comparator starts to compare the ramp generator signal to the input signal  $V_{IN}$ . At the same time the gray code counter counts upwards, and the counter value is stored in the 12-bit register. Both the comparator and the gray code counter use the same clock. When the ramp generator voltage value equals the input signal value, the comparator sends the signal to the register to ignore future values from the gray code counter. When the value of the each step upwards is known the exact input voltage can be solved by multiplying the register value with the ramp generator step value. Figure 13 shows the good linearity of the Wilkinson conversion. After the ADC, the 12-bit values are then transmitted to the SCROD circuit board, and to the main control room. (STURM2 design review, Dr. Gary S. Varner 2009)

FIGURE 13. Wilkinson ADC linearity. Picture Gary S. Varner 2009. STURM2 design review

## 6 STURM2 Firmware

The firmware for the STURM2 ASIC was developed by Larry L. Ruckman in 2007. Before implementing the firmware to all of the eight ASIC boards, it is important to test the firmware and perform necessary updates and debugging.

The design environment in this case was Xilinx ISE, and coding language used was VHDL. Physical devices in the testing phase included a unique STURM2 evaluation board, designed at the Instrumentation Development Laboratory along with the STURM2 ASIC chip. The evaluation board allows a direct connection from the ASIC to PC, allowing programming and readout functions. The board also has an input connector for the signal testing. The testing setup was the following:

A signal generator was used to create the input signal, a high frequency sine wave in this case. When the actual x-ray beam passes the sensor, its profile is very close to the sine wave profile, as shown on Graph 1. The same input signal would also be used as a trigger signal that starts the measurement. The testing would focus on single shot testing, in which the evaluation board would stop taking new measurements after one full measurement. Adjusting the constant values in VHDL it is possible to test several different performance values. To readout the data from the ASIC chip, specially designed readout software was used. This software was designed by the same person as the ASIC firmware, Larry L. Ruckman. (STURM-based x-ray Monitor Meeting page)

The testing of the ASIC chip firmware included following steps:

- Sampling rate

- The sampling rate would be raised by giving a new value for the sample rate constant in the VHDL code after each successful measurement until ASIC could no longer keep up.

- > DAC linearity

- The evaluation board would be connected to the ramp generator, which generates a voltage that increases at each step. The readout software has a function that automatically plots the results. The software is given the value of how much the ramp generator ups the voltage in each step, and the software compares that result to the measured values.

- Analog bandwidth

- Signal generator frequency is raised after each successful measurement to the point where the ASIC could no longer produce a good quality profile of the beam. The result of the ASIC would be compared to one taken by a high quality oscilloscope.

- > Signal noise

- The exact signal amplitude would be measured in a shielded environment with a high precision oscilloscope. The same measurement would be done again in unshielded environment.

- > 3 dB frequency

- Signal generator frequency is raised after each successful measurement to the point where the output signal value drops 3 dB.

- > Time base VS temperature

- Measurements above would be taken again, this time the evaluation board would be cooled / warmed between measurements.

The STURM2 evaluation board is unique device, and only two boards are ever made, one located in KEK High Energy Physics Laboratory in Tsukuba Japan, and other in the Instrumentation Development Laboratory in University of Hawaii. When starting the test physical setup, the STURM2 evaluation board could not be located, despite the IDLab has storage unit with very good inventory of all the devices. Last person to use that had obviously misplaced the board. To get the physical setup completed, the other existing board had to be flown in from Tsukuba Japan, with expensive rush air cargo delivery. After the physical testing setup was in place and the test steps were agreed a number of very serious issues were discovered. To begin with, the firmware VHDL code was broken into dozens of fragments each located in an individual file. To understand how these small fragments came to together to form a functioning firmware requires a careful examining the firmware documentation. In this case, no such documentation existed. Also, the code does not include a single comment line, and many of the signal names and variables were named differently than what was decided at the beginning of the STURM2 project.

The lack of the documentation and comment lines, along with differently named variables made understanding the full function of the firmware extremely difficult. However, with the help of good readout software, it is possible to understand the function quicker by making changes in the VHDL code and examining the effects that they have on the ASIC readout.

The Xilinx ISE design software requires a Windows environment when the STURM2 readout software was designed to be used in a Linux environment. Several different attempts were made to get both of the software to run under one and the same environment, which caused a big delay in the testing process. Eventually it became clear that it was impossible to do so with the equipment in hand. Attempts were made to test the firmware by first examining the code under the Windows environment, and then change to the Linux environment for testing. This kind of working method is extremely slow and ineffective. When combining this with the time it took for the readout software to process all the test data, it was possible to make only few changes a day into the firmware code. As a result of all these issues, the firmware testing was postponed until more suitable testing software could be used.

The issues discovered during the firmware testing were by far the biggest setback during this thesis. But on the other hand, it does serve as a very good example of the way things should not be done. When one person only focuses on his own work and fails to realize the demands and goals of the entire project, the results are unsatisfactory at best. After all these issues were explained to all the people involved in the project, another worker had to be brought in to try make the firmware operational again. Now one person's lack of following the project criteria caused a double workload and extra costs, not to mention the time lost when software that was supposed to be finished was not.

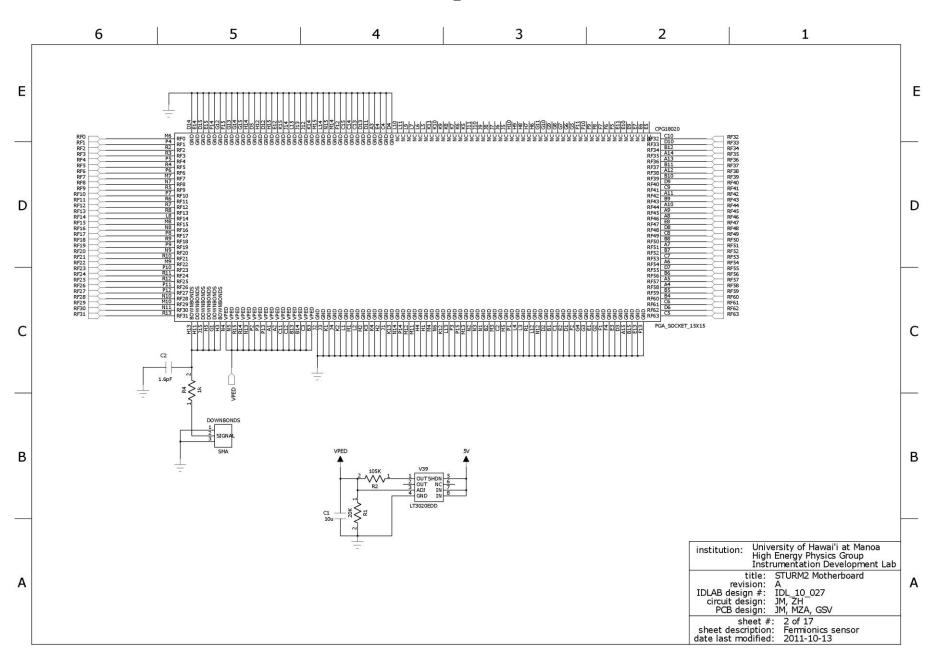

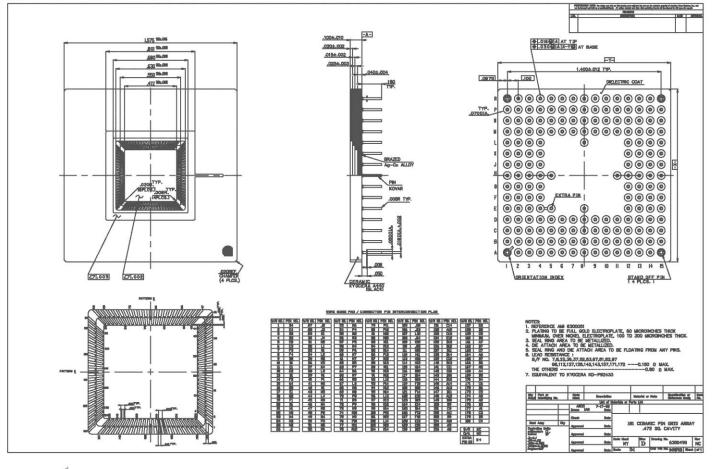

## 7 Fermionics sensor

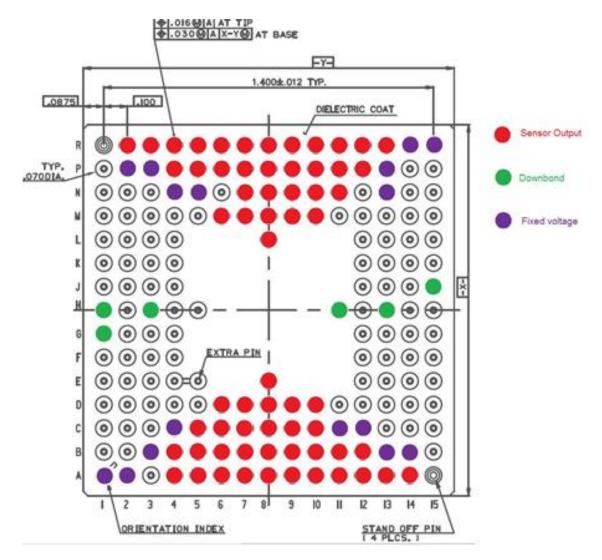

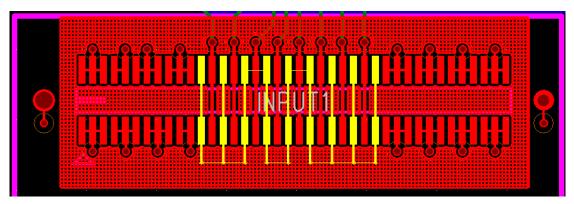

The fermionics sensor is the component that detects the x-ray beams and produces a weak analog voltage signal. The output signal strength and needed amplification is explained in Chapter 2. The fermionics sensor, shown in Figure 14 has 128 detectors. In this design, 64 detectors are used to measure the x-ray beams and 16 detectors are connected to fixed VPED voltage. These 16 detectors with VPED voltage level are located at the edge of the x-ray detectors, eight detectors at both left and the right side. This is to make sure that the unused detectors at the edges of the sensor will not affect the x-ray detectors. The sensor in Figure 14 is already attached to the CPG18020 socket with bonding wires.

FIGURE 14. Fermionics sensor in CPG18020 socket.

The CPG18020 socket holding the sensor is then attached to PGA socket shown in Figure 15, which is fixed on the motherboard. This is a lever action socket, and the CPG18020 that houses the fermionics sensor can be attached and removed from the motherboard by using the locking lever.

FIGURE 15. Lever operated GPA socket

Installing the sensor by this method provides several benefits. A broken sensor can be quickly replaced, and when a more advanced sensor appears in the future, the device can be quickly updated.

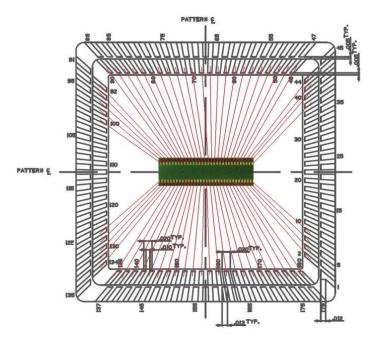

The sensor and both sockets were already manufactured by other companies and were ordered online. The task that remained to be done at the Instrumentation Development Laboratory was to design the most effective bonding option. To accomplish this, there are two main ways of doing it. The first attempt was to design the bonding wires in a way that detector number one on the fermionics sensor would be connected to the lower left corner of the CPG18020 socket, detector number two next to detector one and so on. This would make the routing of the signal line from CPG socket to amplifiers easier and less complex. However, the connection between wire bond pads and connectors in the bottom of the socket are in completely random order. This means that some of the bonding wires between sensor wire bond pads and fermionics sensor detectors would inevitably cross each other, causing short circuits. This design method was found ineffective. More detailed information about connections between the wire bond pads and socket bottom connector pins can be found in Appendix 7.

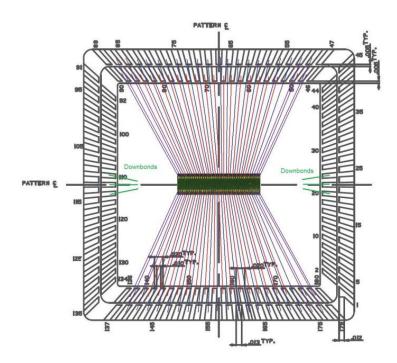

The other way of designing the bonding wires is to focus on keeping the bonding wires as far away from each other as possible, and completely ignore the bottom connector pins. However, in this kind of approach two other design criteria's must be taken into count. The angle of which the bonding wires connect to the fermionics sensor detectors must be kept as low as possible for better performance.

Also, the wire bonding pads on the socket are located at two different heights. If both the upper and lower row is used, some of the wires would be in top of the lower row. This limited the bonding options into two. The first one allows a higher connection angle and avoid bonding wires to be placed into two different heights, which is shown in Figure 16.

FIGURE 16. Fermionics sensor bonding option 1.

The second is keeping the connection angle as small as possible and allowing the bonding wires to be placed into two different heights, risking a short circuit in case one the upper wires would come loose, shown in Figure17.

FIGURE 17. Fermionics sensor bonding option 2.

After consulting with experts at the company which would do the wire bonding, option two were the focus is in minimal connection angles was decided to be the better of these two. In addition to the x-ray detector bonding wires the fixed VPED voltage wires for 16 detectors and six down bond wires were added to design. These down bond wires will be connected to the external voltage source with an SMA connector, thereby enabling an adjusted voltage level. The purpose of these down bond wires is very similar to VPED wires, to keep the bottom plane of the CPG18020 socket at a constant voltage. Finally, a map of the socket bottom pins was created to ease the routing planning. This map is shown in Figure 18. (STURM-based x-ray Monitor Meeting page.)

FIGURE 18. CPG18020 pin map.

The actual routing is explained in more detail in Chapter 8.

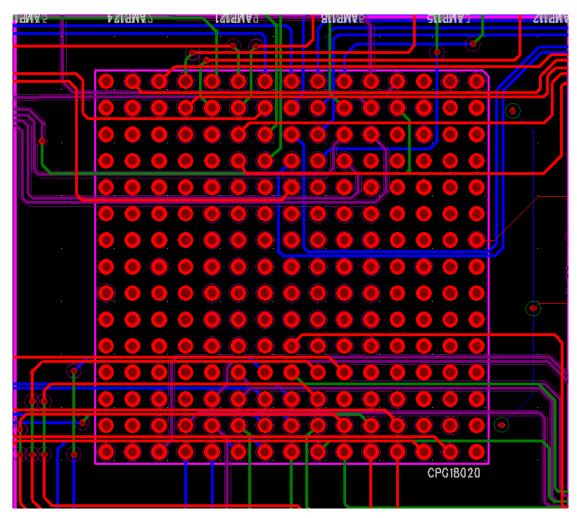

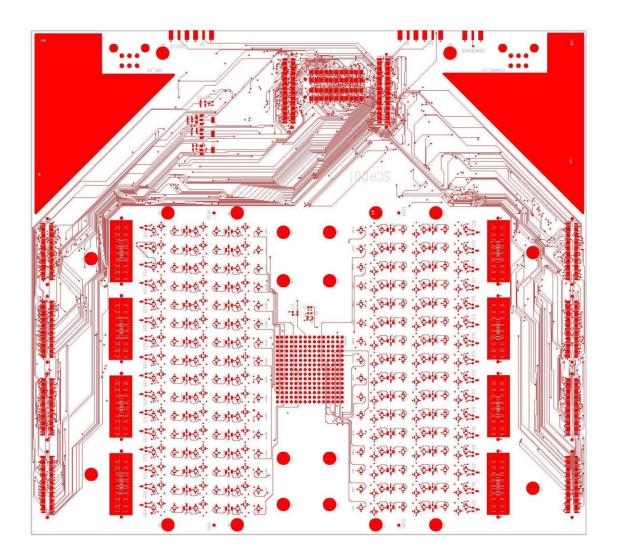

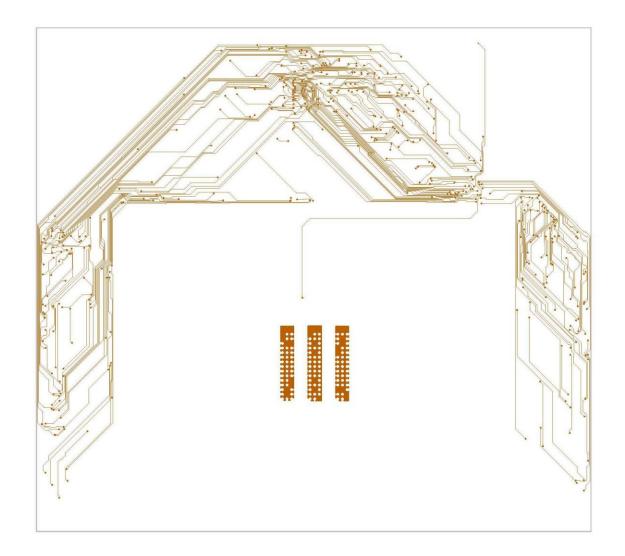

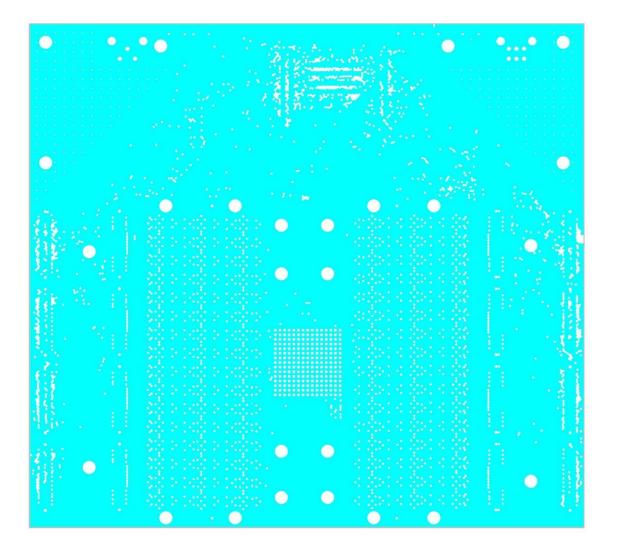

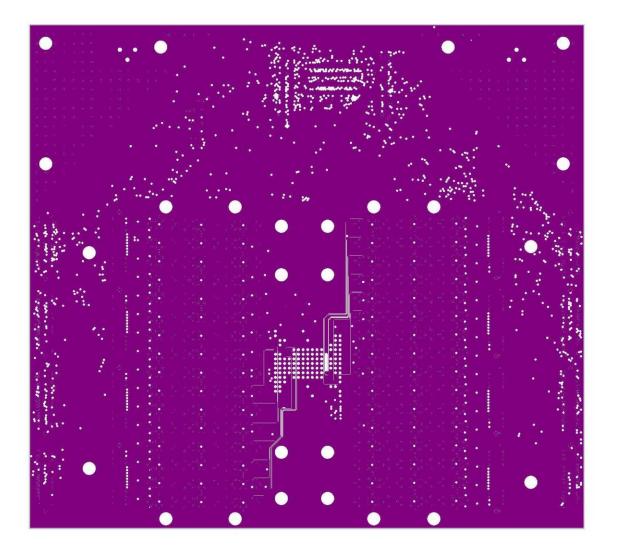

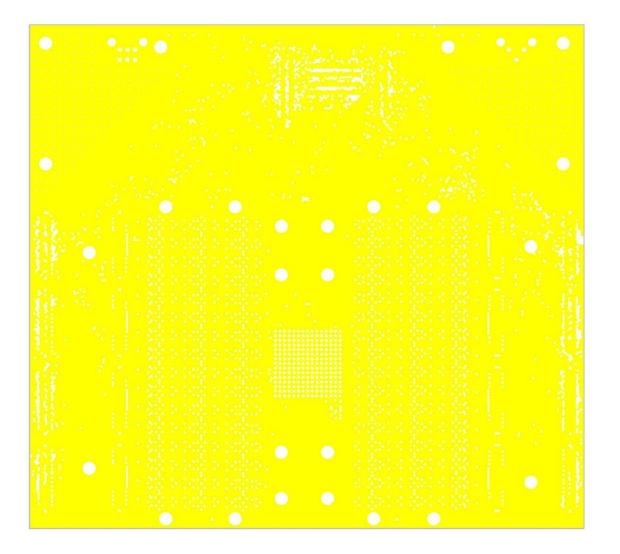

## 8 Motherboard

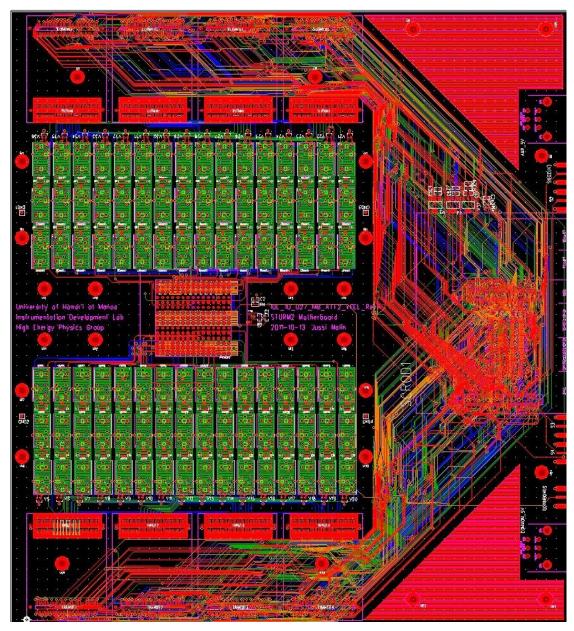

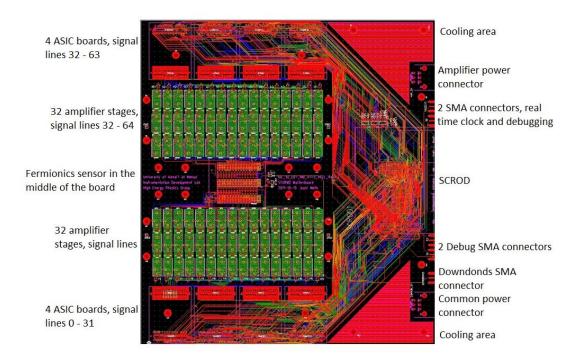

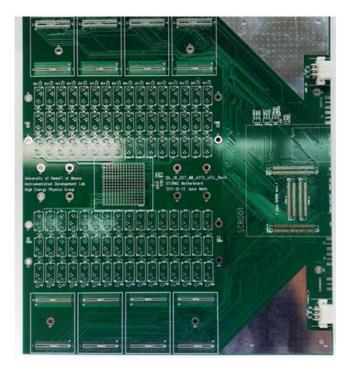

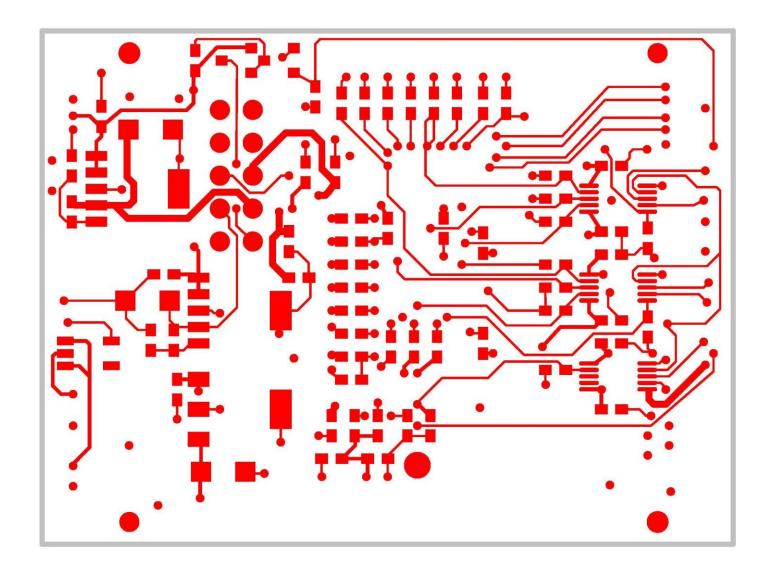

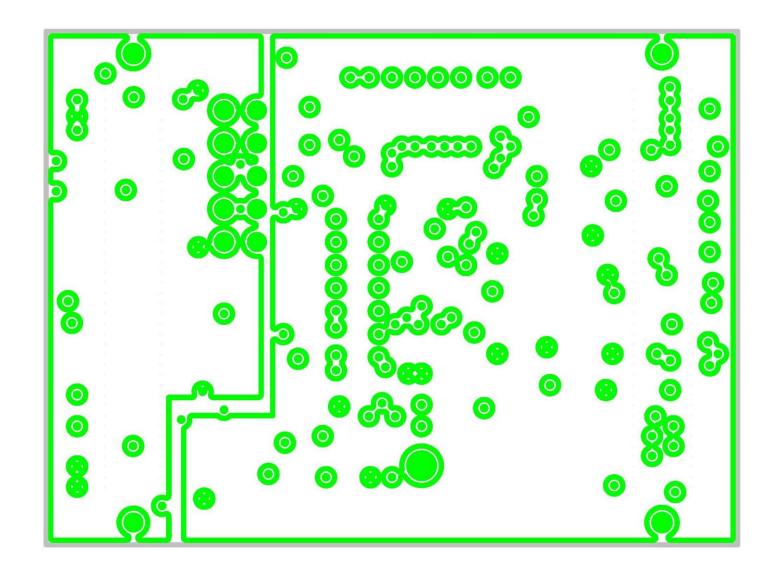

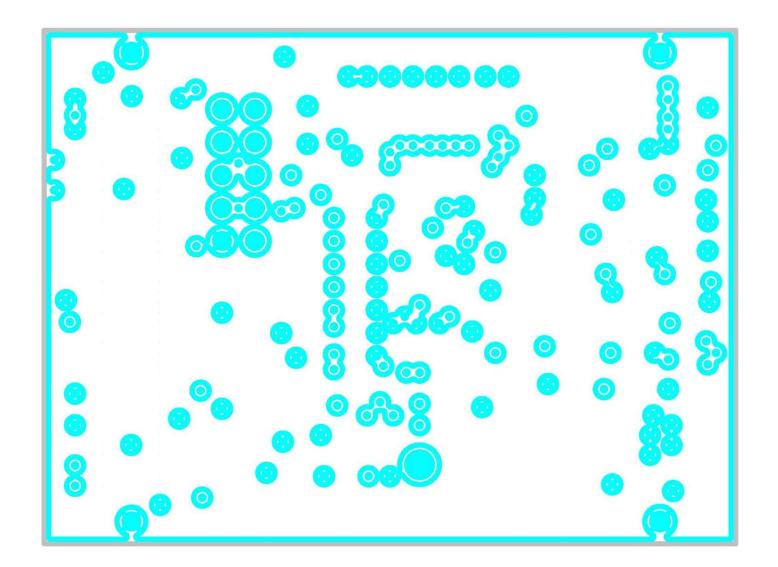

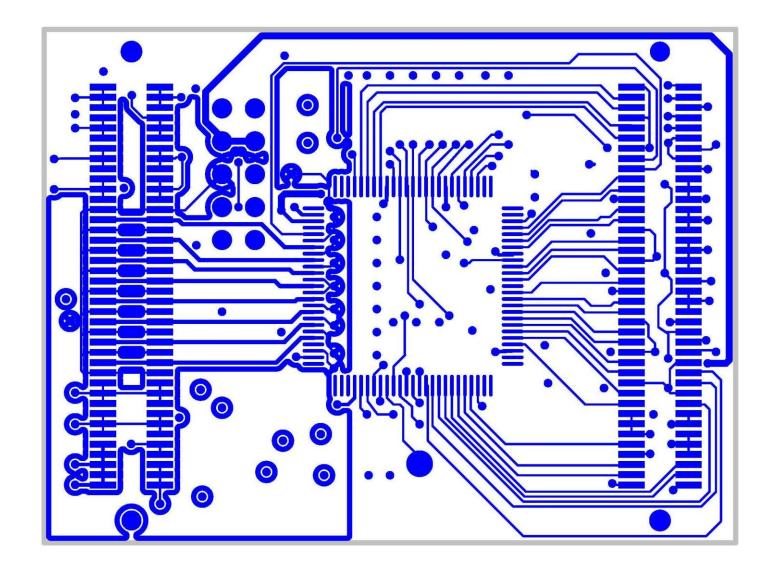

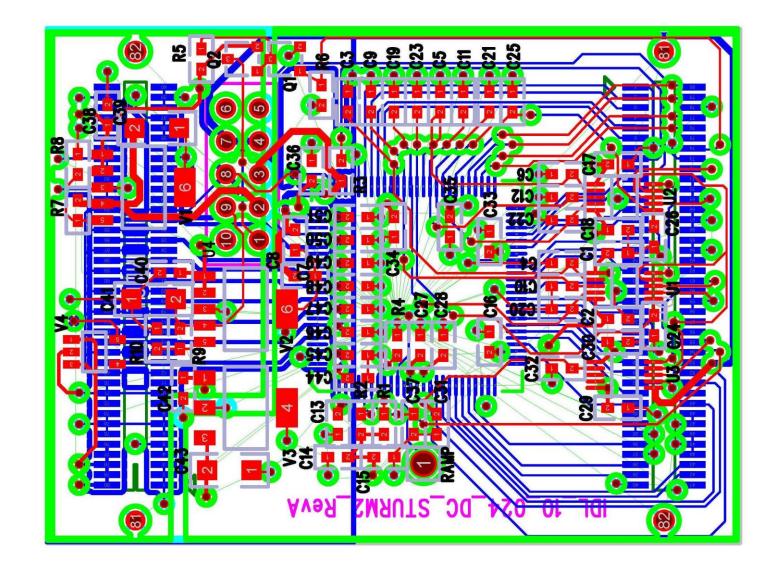

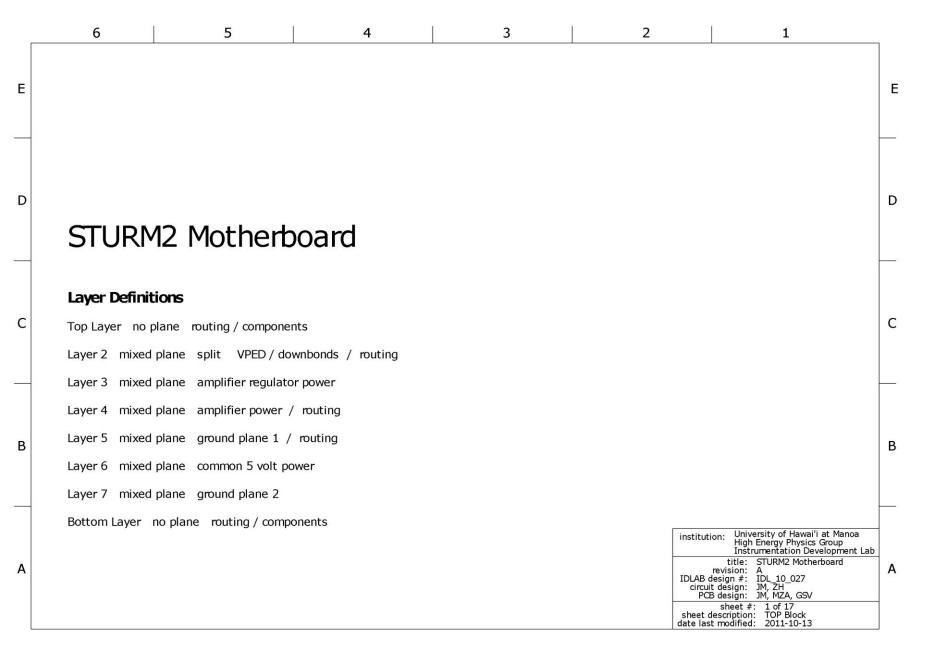

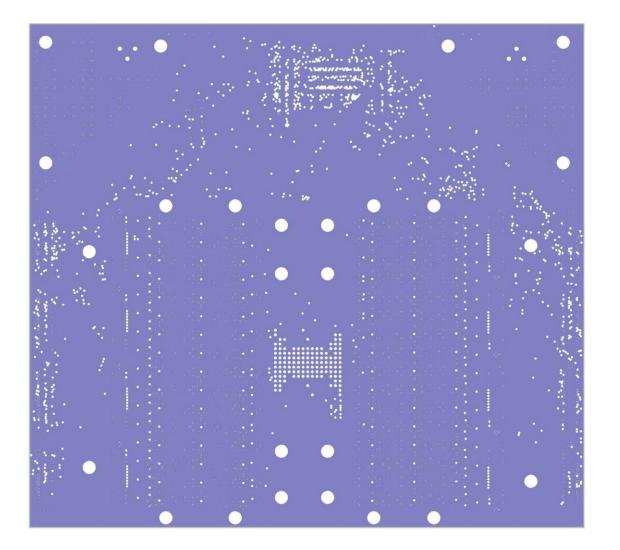

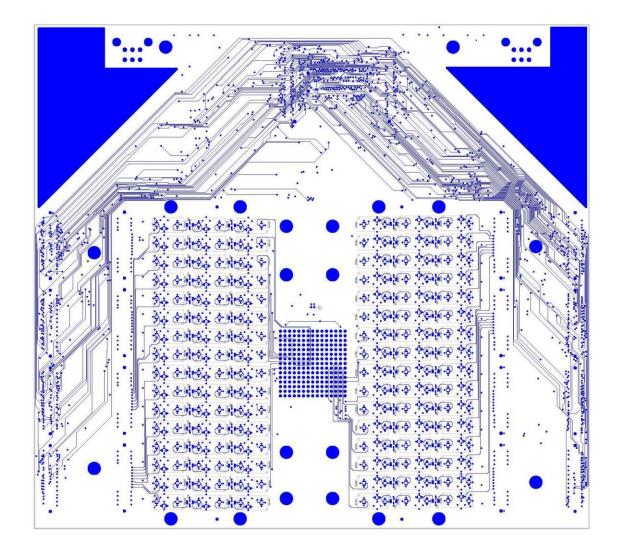

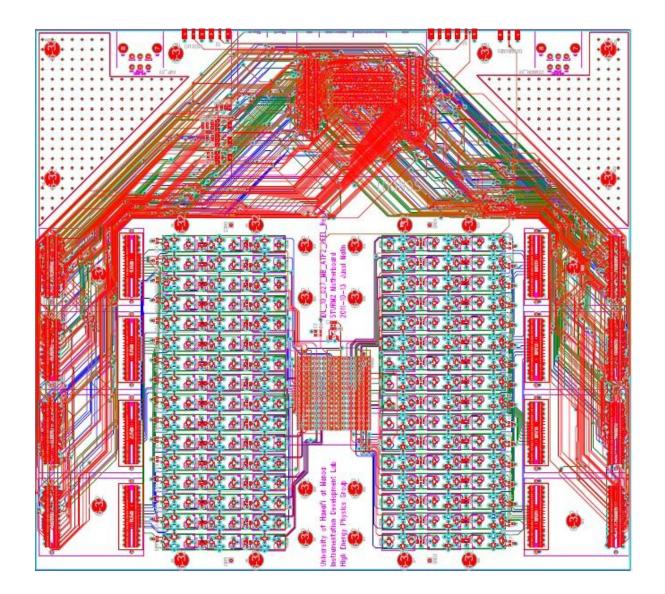

The STURM2 Motherboard is the largest and most complex circuit board in the device, and also the main focus in this thesis. The function of the motherboard is to house all the STURM2 components, provide all necessary voltage levels and power for the other circuit boards, and allow physical attachment to the Super-KEKB. (STURM-based x-ray Monitor Meeting page.) The main features of the motherboard are following:

- Board dimensions 10.9 X 12 inches

- Eight electrical layers

- Houses all other STURM2 circuit boards and components

- 192 Amplifier boards

- Eight ASIC boards

- One fermionics sensor

- SCROD

- Two power connectors

- Five SMA connectors